CH32V307时钟为144MHz,PCLK2时钟也为144MHz,而我看手册ADC最大时钟为14MHz,即便给最大的那个分频8分频也降不到14MHz啊,只能降低PCLK2的时钟了吗

查看: 861

回复: 7

CH32V307 ADC

热门产品 :

CH339: 7端口多功能USB HUB控制器芯片

只能降低PCLK2的时钟的话怎么改呢

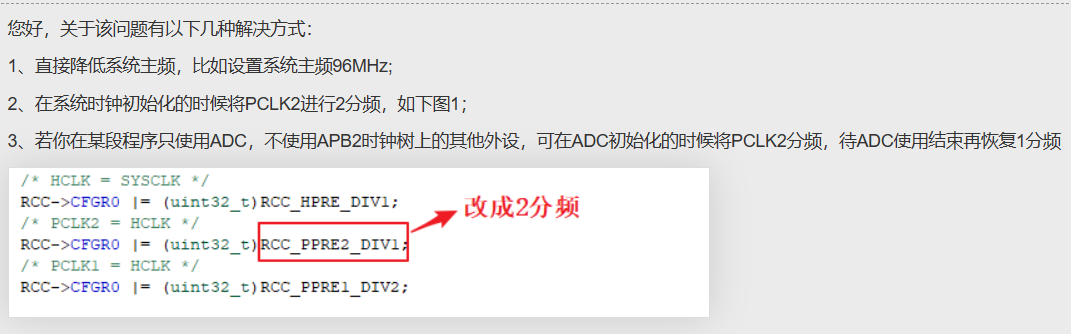

您好,关于ADC时钟和系统主频之间的处理问题,可以参考一下下帖回复。关于降低PCLK2的时钟,可在配置系统主频的函数中修改PCLK2的时钟分频,修改成2分频即可。后续若有问题,可通过邮箱(lzs@wch.cn)和我沟通。

逐飞的程序好像直接忽略了这个限制,给的巨高无比,并表示可以用,问题不大,请问这样有什么潜在的问题吗

您好,建议按照手册要求使用,ADC输入时钟最大限制在14MHz内,这边没有按照你说的用过,可能会存在一些问题,为了代码稳定运行,不建议这么用。

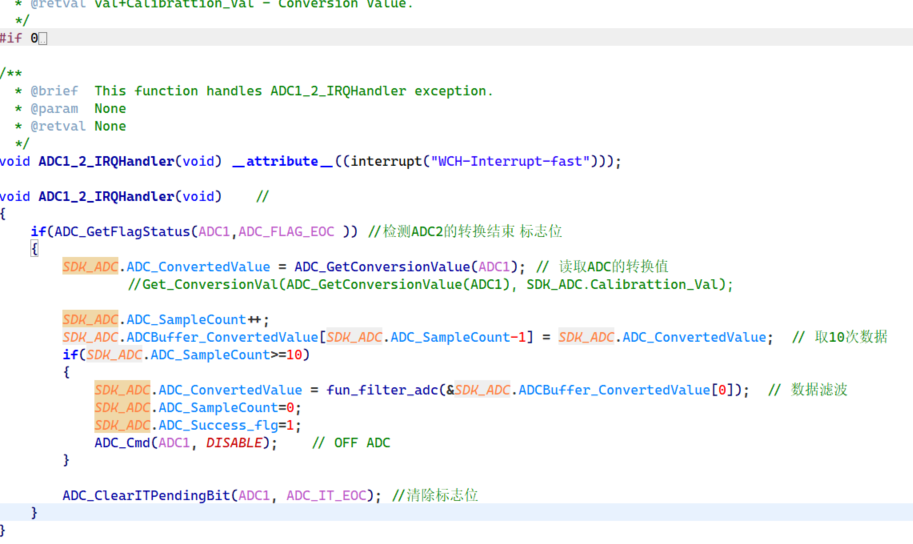

V307 ADC 连续单通道模式:每轮结束后重复新一轮的转换。只有进入中断ADC1_2_IRQHandler 一次,不能连续重复进入中断。暂时退步求其次,使用轮询。什么原因,请原厂分析一下。

附上图,如下;

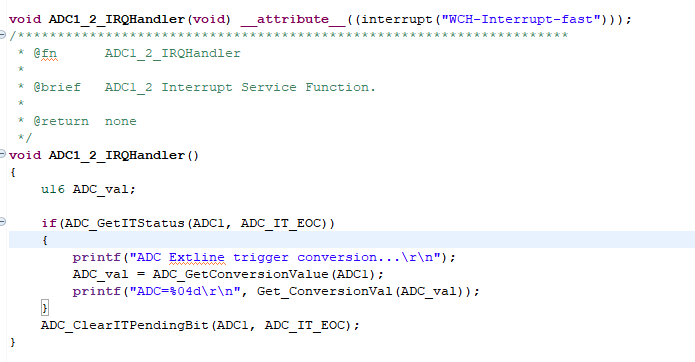

您好,若方便可以把ADC部分完整工程发至我的邮箱(lzs@wch.cn)看一下,单看截图应该没问题,可以参考一下下图

请勿发布广告和违法内容, 代码可以选择编辑器代码语言格式, 更易他人阅读帮助您, 或者留下联系方式,以便更好更快服务您

只有登录才能回复,可以选择微信账号登录