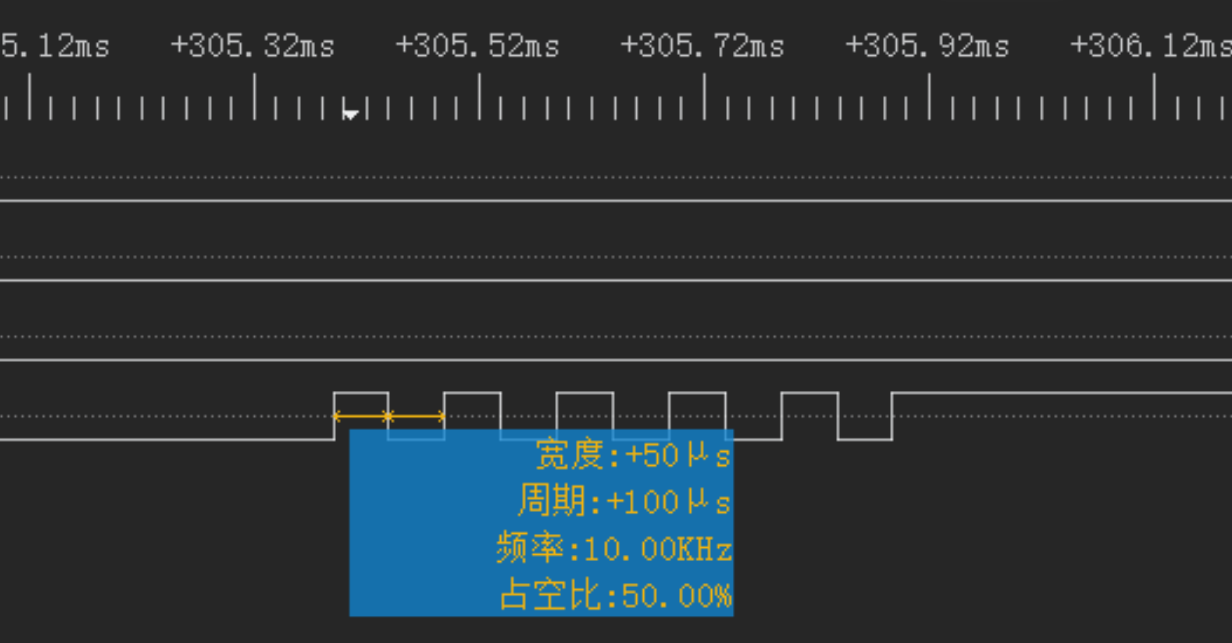

CH582在配置timer做PWM输出的时候可以配置输出PWM波的极性;但是发现了一个这样的问题:

就是在配置极性默认高电平,低电平有效的时候,当PWM输出使能的时候都符合逻辑没问题,但是当PWM输出使能关闭的时候,此时测得这个IO口的输出是低电平;反之如果开始之前配置的极性是默认低电平,高电平有效的情况在PWM输出使能关闭的时候测得这个IO抠输出是高电平。难道在关闭PWM使能之后不应该保持默认电平吗?难道在关闭后内部有取反电路?

CH582在配置timer做PWM输出的时候可以配置输出PWM波的极性;但是发现了一个这样的问题:

就是在配置极性默认高电平,低电平有效的时候,当PWM输出使能的时候都符合逻辑没问题,但是当PWM输出使能关闭的时候,此时测得这个IO口的输出是低电平;反之如果开始之前配置的极性是默认低电平,高电平有效的情况在PWM输出使能关闭的时候测得这个IO抠输出是高电平。难道在关闭PWM使能之后不应该保持默认电平吗?难道在关闭后内部有取反电路?

有没有大佬解释一下的,我翻阅了手册没看到有相关的电路或者文字可供参考。

你好,如果在关闭PWM功能之后,注意将对应的GPIO的功能使能位也关闭。然后重新对该gpio进行 GPIO的初始化,给一个固定的电平状态即可,如配置pp输出并拉高电平。这是比较稳妥的方式。

您好,“如果在关闭PWM功能之后,注意将对应的GPIO的功能使能位也关闭。”,这句话的意思是关闭PWM之后,仍需要关闭输出使能中断使能这些功能之后再配置GPIO初始化是吗?那意思是直接关闭PWM的输出之后,不做其他处理,此时的IO口的电平是不可预测的吗?

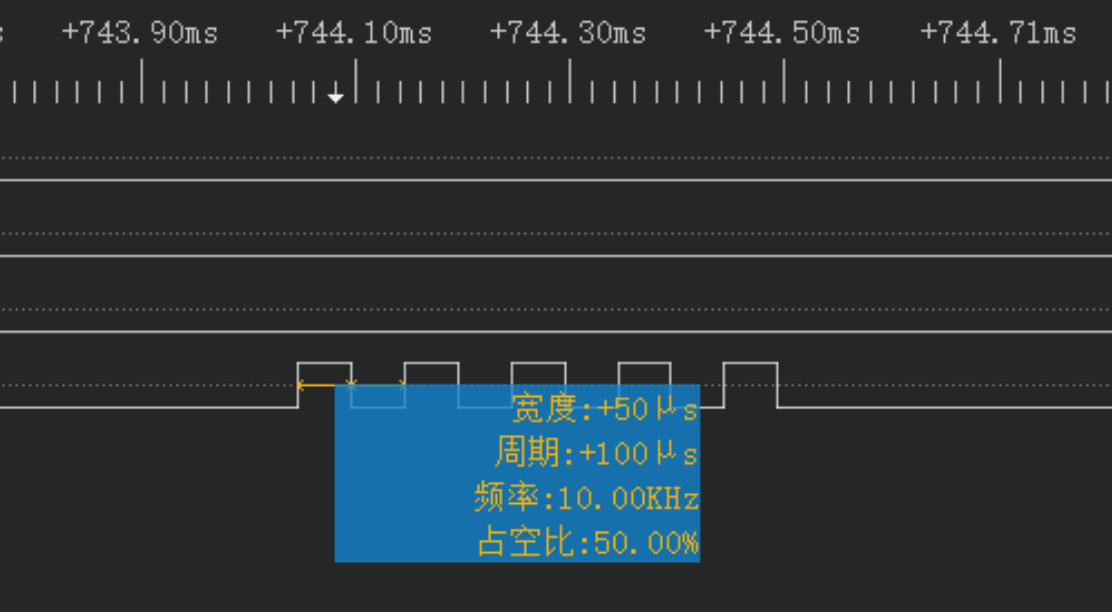

您好,定时器输出PWM,若启停时间点不确定,停止在高电平还是低电平也是不确定的,可以在停止后手动调用GPIOx_ResetBits拉低/GPIOA_SetBits拉高。

好的,感谢答复。