条件:

使用USB,只需要FS(12Mbps)。

系统不存在“待机模式”等低功耗场景。

GPIO实现TDM接口。TDM打算使用TIM实现,TIM_CLK=4.096MHz,生成2.048MHz时钟和8KHz脉冲(宽度2.048MHz时钟一拍)。TDM接口有收发两组接口,以发送接口为例:TX_Fr、Tx_bclk、Tx_Dat,三个信号同步;接收接口(RX_Fr、Rx_bclk、Rx_Dat)同理。

问题

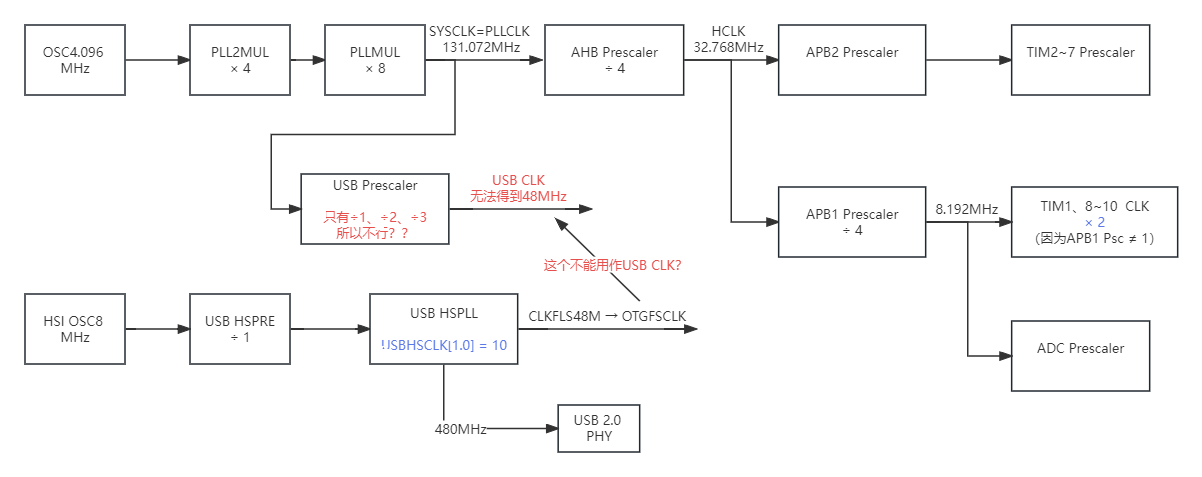

HSE打算使用4.096MHz,USB使用HSI的8M,SYSCLK由HSE→PLL2MUL(×4)PLLMUL(×8)产生,即SYSCLK = HSE(4.096)× PLL2(4)×PLL(8)= 131.072MHz,如下述图1。以上设计是否可行?(因RM手册P24的图3-2最下方有一句“当使用 USB 功能时,CPU 的频率必须是 48MHz、?96MHz 或 144MHz。”)

如a不可行,打算外部生成4.096MHz(Tx_bclk、Rx_bclk)时钟和8K(Tx_Fr、Rx_Fr)脉冲,将这两种时钟送给TIM,用TIM触发相应的事件以后进行特定的处理。是否直接使用EVT SDK中 “TIM/Input_Capture”例程?