CH32V203的ADC时钟疑问

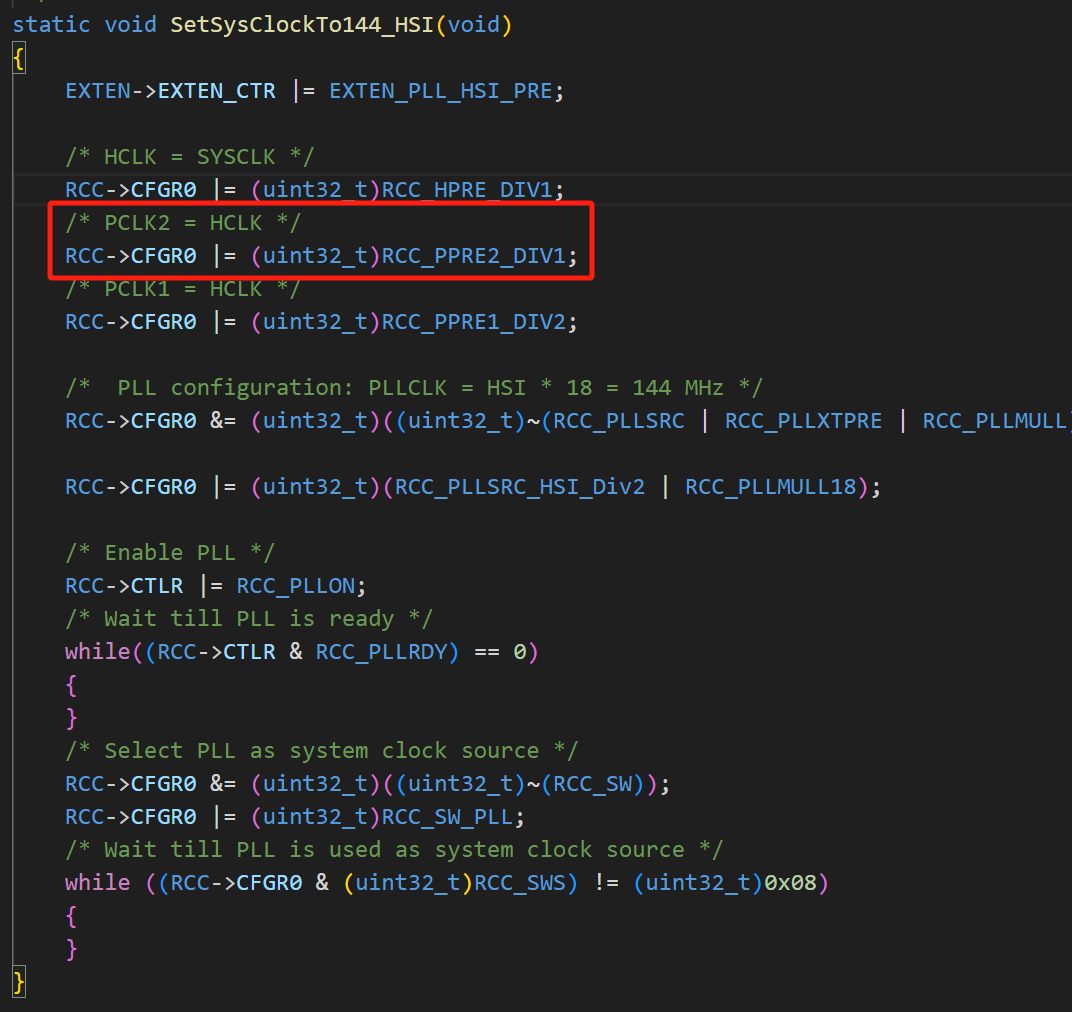

从系统时钟树上来看,ADC的时钟来源是PCLK2,看了时钟的初始化,使用144MHz

PCLK2等于144MHz,ADC的最大分频是8分频,也就是18MHz,而规格书说明,ADC时钟最大不能超过14MHz,这个怎么解决?

热门产品 :

CH32V317: 互联型青稞RISC-V MCU

CH32V203的ADC时钟疑问

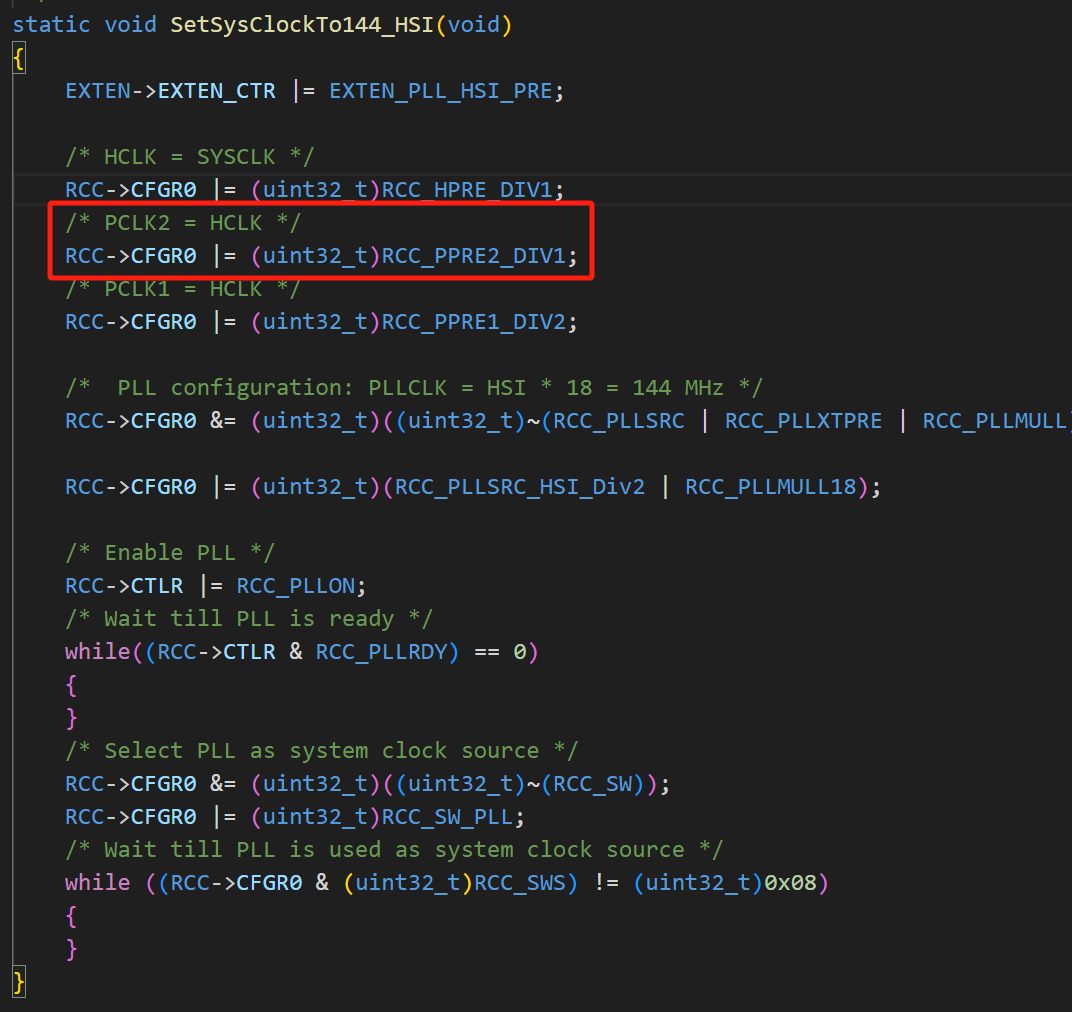

从系统时钟树上来看,ADC的时钟来源是PCLK2,看了时钟的初始化,使用144MHz

PCLK2等于144MHz,ADC的最大分频是8分频,也就是18MHz,而规格书说明,ADC时钟最大不能超过14MHz,这个怎么解决?

使用的时候降频,不适用的时候恢复, RCC->CFGR0 |= (uint32_t)RCC_PPRE2_DIV2; RCC->CFGR0 |= ~(uint32_t)RCC_PPRE2_DIV2;或者主频96M,8分频。

那我一直设置PCLK2二分频,这样没啥问题吧?

那也没问题,但是计算挂载在APB2时钟总线上的时钟都分频了,需要注意一下。