CH32V208如何设置低于48MHz时钟?

在例程中,最低只有48MHz,如何更低?

另外请问有没有CH32V208CBU6?(QFN48)的 原理图和PCB的封装库? ?邮箱 个人信息保护,已隐藏

CH32V208如何设置低于48MHz时钟?

在例程中,最低只有48MHz,如何更低?

另外请问有没有CH32V208CBU6?(QFN48)的 原理图和PCB的封装库? ?邮箱 个人信息保护,已隐藏

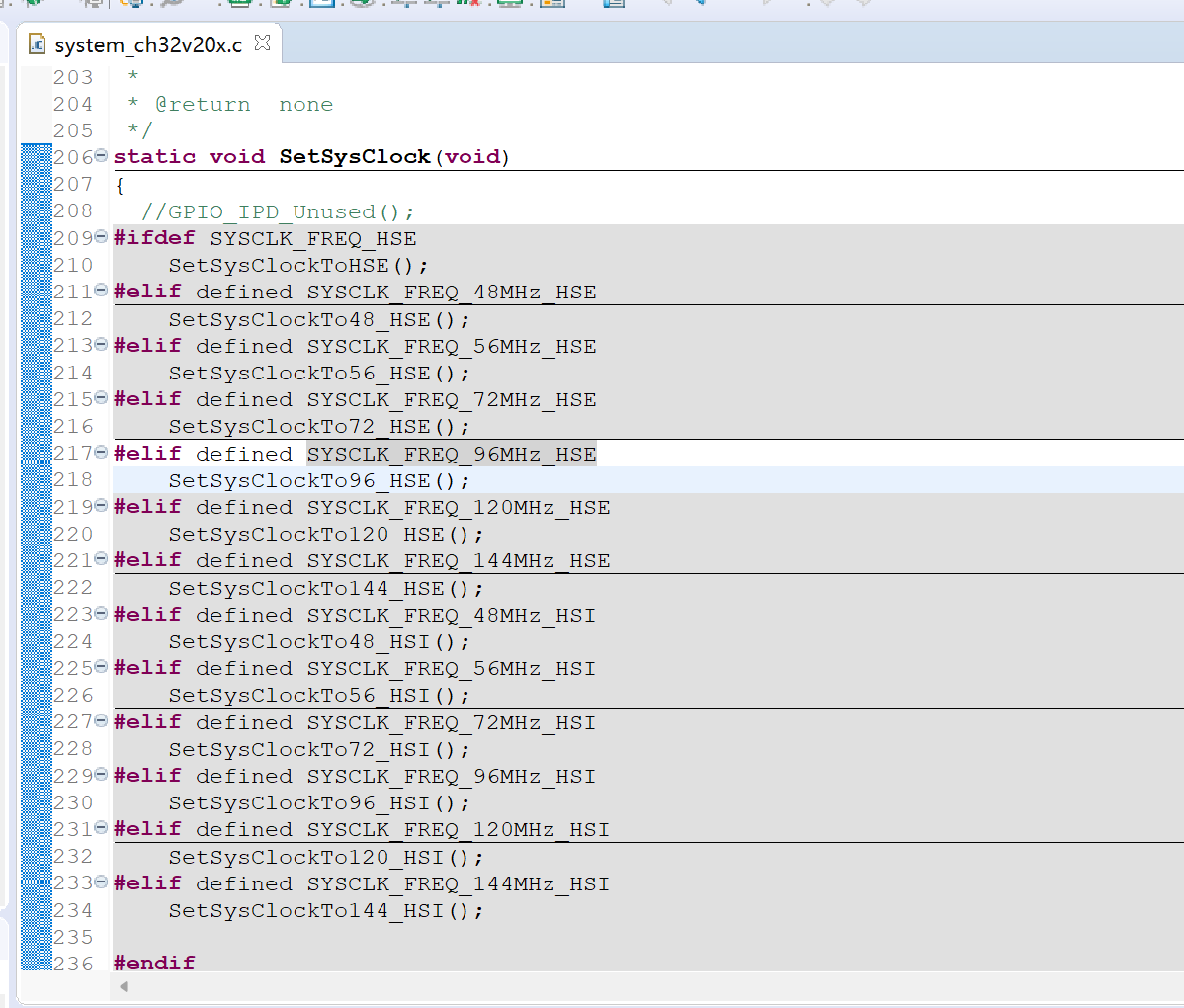

CH32V208的flash不是128k吗?编译例程程序SpeedTest_Peripheral显示448k?请问是数据手册错了吗?

make -j20 all

Memory region Used Size Region Size %age Used

FLASH: 162080 B 448 KB 35.33%

RAM: 15820 B 64 KB 24.14%

text data bss dec hexfilename

160976 1104 14716 176796 2b29cSpeedTest_Peripheral.elf

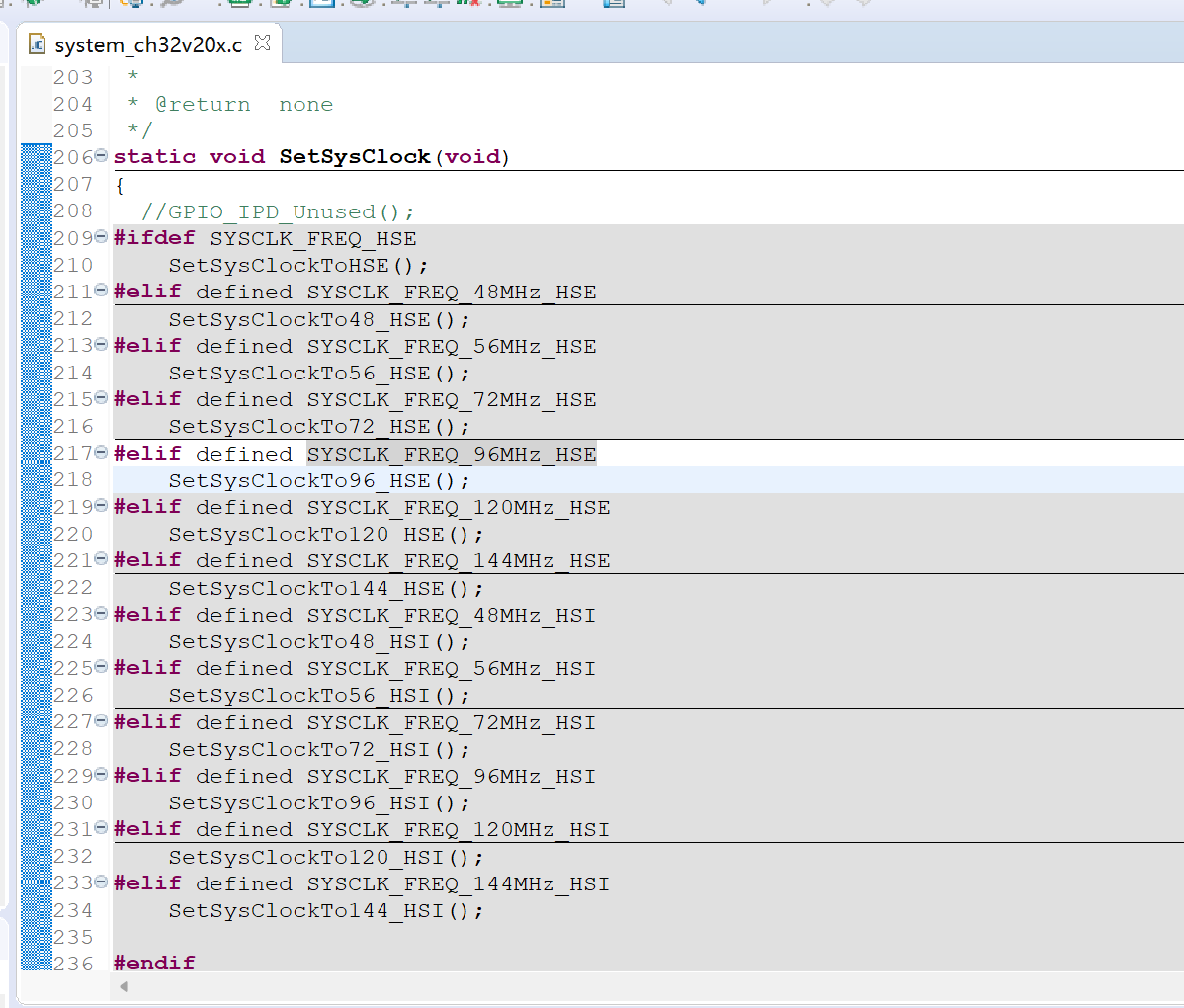

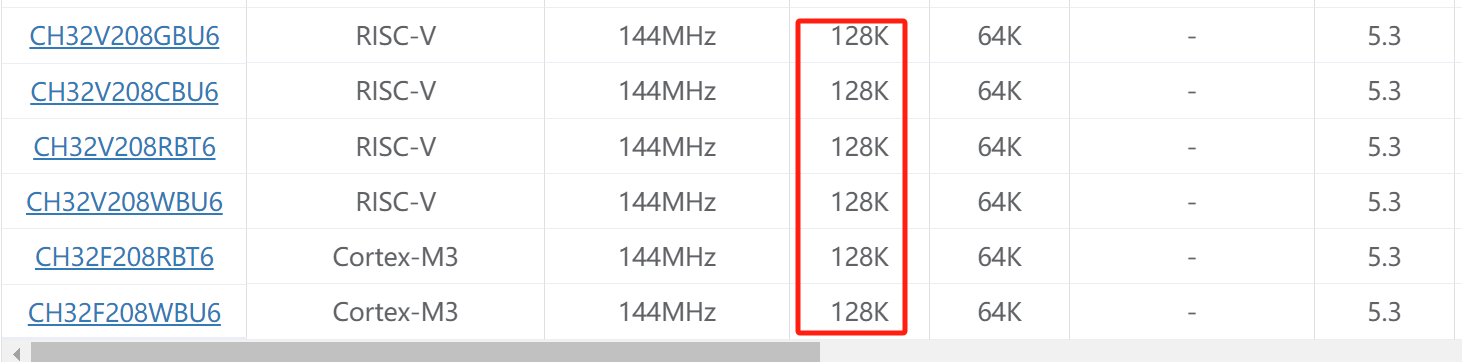

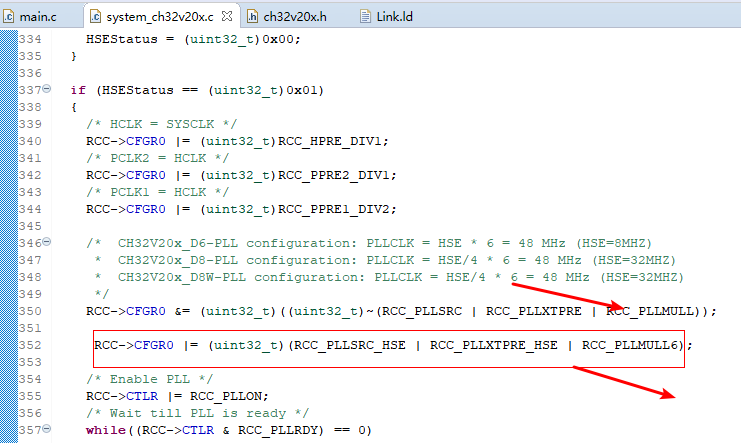

您好,例程中,可直接通过修改相关宏定义,将系统主频配置成HSE,即32MHz,如下图1。主频想要配置其他大小,可通过修改分频系数配置,如下图2。下链接为MCU封装库下载链接。原理图在EVT PUB文件夹下有。关于V208的FLASH,分为零等待区域和非零等待区域,共480K,具体看数据手册。

图1

图2

好的,谢谢。

就是把RCC_PLLMULL6 改成 RCC_PLLMULL2就可以获得16MHz的时钟。另外还有3个问题:

(1)RCC_PLLMULL2 这个最小是2倍频,可以1倍频吗? /4 是哪里配置的呢?是 RCC_PLLXTPRE_HSE 这个吗 ?然后 RCC_PLLXTPRE_HSE_Div2 这个是除以8? 这样最低频率是8MHz?

如果增加新的频率 我是不是应该也写上对于宏定义?

#define SYSCLK_FREQ_8MHz_HSE 8000000

#elif defined SYSCLK_FREQ_8MHz_HSE

uint32_t SystemCoreClock = SYSCLK_FREQ_8MHz_HSE; /* System Clock Frequency (Core Clock) */

这样串口蓝牙等初始化就可以直接用了。

(2)是不是我在执行程序时候可以在需要高速时切换到高速频率运行,低速时切换至很低的频率 以节省电能。切换主频时初始化所有和主频相关的外设。

(3)Flash 零等待区域,是不是像ram一样的运行速度?

您好,关于你的问题:

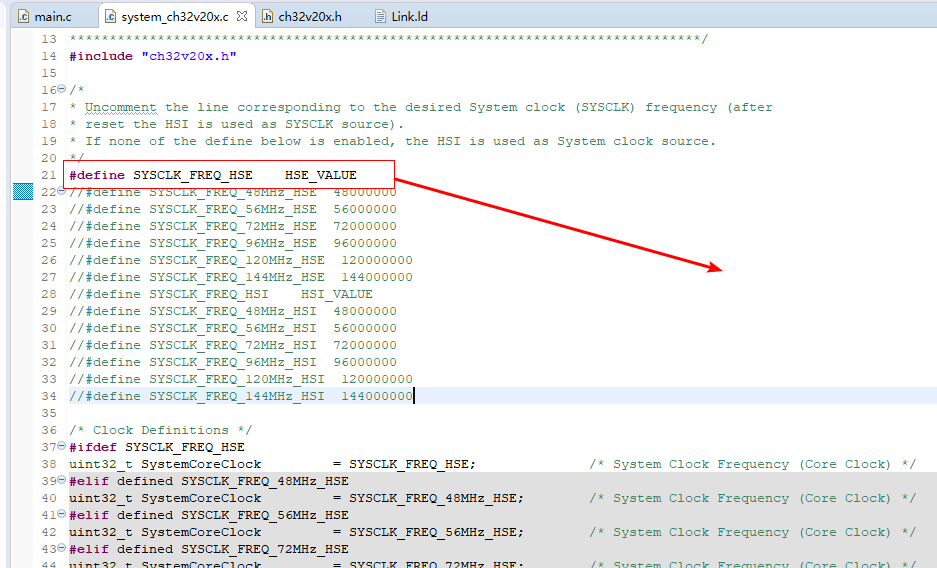

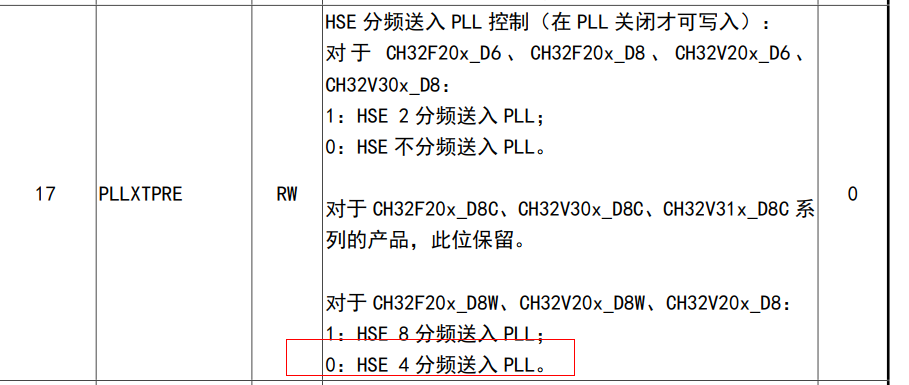

(1)最小2倍频;/4是对时钟配置寄存器0位17的配置,如下图1;是除以8,可配置8MHz。不是你这么定义配置的,可参考48MHz主频的配置;

(2)切换时可以直接调用系统主频初始化配置函数重新初始化,相关外设可以再初始化一遍;

(3)是的

图1