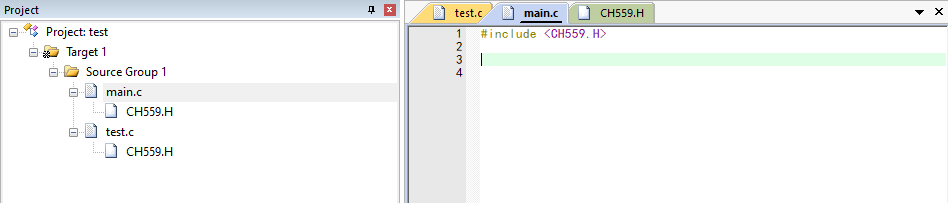

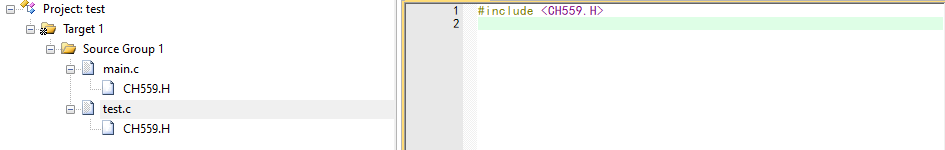

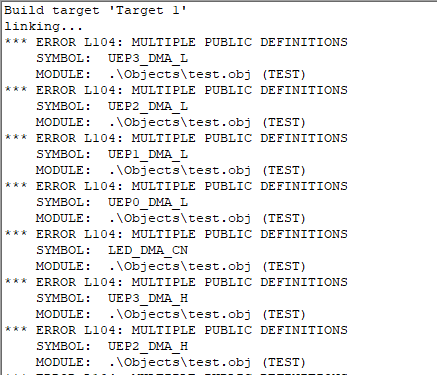

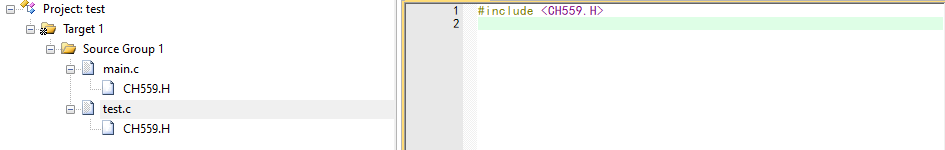

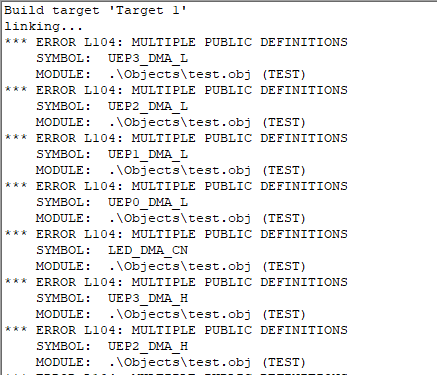

如上图所示,在main.c和test.c中同时引用Ch559.H头文件,就会报 ERROR L104: MULTIPLE PUBLIC DEFINITIONS相关错误,请问这个问题该如何解决?

如上图所示,在main.c和test.c中同时引用Ch559.H头文件,就会报 ERROR L104: MULTIPLE PUBLIC DEFINITIONS相关错误,请问这个问题该如何解决?

EXTERN? UINT8XV UEP4_1_MOD? ? ?_AT_ 0x2446;? ?// endpoint 4/1 mode

#define pUEP4_1_MOD? ? ? ?PBYTE[0x46]

#define bUEP1_RX_EN? ? ? ?0x80? ? ? // enable USB endpoint 1 receiving (OUT)

#define bUEP1_TX_EN? ? ? ?0x40? ? ? // enable USB endpoint 1 transmittal (IN)

#define bUEP1_BUF_MOD? ? ?0x10? ? ? // buffer mode of USB endpoint 1

// bUEPn_RX_EN & bUEPn_TX_EN & bUEPn_BUF_MOD: USB endpoint 1/2/3 buffer mode, buffer start address is UEPn_DMA

//? ?0 0 x:? disable endpoint and disable buffer

//? ?1 0 0:? 64 bytes buffer for receiving (OUT endpoint)

//? ?1 0 1:? dual 64 bytes buffer by toggle bit bUEP_R_TOG selection for receiving (OUT endpoint), total=128bytes

//? ?0 1 0:? 64 bytes buffer for transmittal (IN endpoint)

//? ?0 1 1:? dual 64 bytes buffer by toggle bit bUEP_T_TOG selection for transmittal (IN endpoint), total=128bytes

//? ?1 1 0:? 64 bytes buffer for receiving (OUT endpoint) + 64 bytes buffer for transmittal (IN endpoint), total=128bytes

//? ?1 1 1:? dual 64 bytes buffer by bUEP_R_TOG selection for receiving (OUT endpoint) + dual 64 bytes buffer by bUEP_T_TOG selection for transmittal (IN endpoint), total=256bytes

#define bUEP4_RX_EN? ? ? ?0x08? ? ? // enable USB endpoint 4 receiving (OUT)

#define bUEP4_TX_EN? ? ? ?0x04? ? ? // enable USB endpoint 4 transmittal (IN)

// bUEP4_RX_EN & bUEP4_TX_EN: USB endpoint 4 buffer mode, buffer start address is UEP0_DMA

//? ?0 0:? single 64 bytes buffer for endpoint 0 receiving & transmittal (OUT & IN endpoint)

//? ?1 0:? single 64 bytes buffer for endpoint 0 receiving & transmittal (OUT & IN endpoint) + 64 bytes buffer for endpoint 4 receiving (OUT endpoint), total=128bytes

//? ?0 1:? single 64 bytes buffer for endpoint 0 receiving & transmittal (OUT & IN endpoint) + 64 bytes buffer for endpoint 4 transmittal (IN endpoint), total=128bytes

//? ?1 1:? single 64 bytes buffer for endpoint 0 receiving & transmittal (OUT & IN endpoint)

//? ? ? ? ? ?+ 64 bytes buffer for endpoint 4 receiving (OUT endpoint) + 64 bytes buffer for endpoint 4 transmittal (IN endpoint), total=192bytes

EXTERN? UINT8XV UEP2_3_MOD? ? ?_AT_ 0x2447;? ?// endpoint 2/3 mode

#define pUEP2_3_MOD? ? ? ?PBYTE[0x47]

#define bUEP3_RX_EN? ? ? ?0x80? ? ? // enable USB endpoint 3 receiving (OUT)

#define bUEP3_TX_EN? ? ? ?0x40? ? ? // enable USB endpoint 3 transmittal (IN)

#define bUEP3_BUF_MOD? ? ?0x10? ? ? // buffer mode of USB endpoint 3

#define bUEP2_RX_EN? ? ? ?0x08? ? ? // enable USB endpoint 2 receiving (OUT)

#define bUEP2_TX_EN? ? ? ?0x04? ? ? // enable USB endpoint 2 transmittal (IN)

#define bUEP2_BUF_MOD? ? ?0x01? ? ? // buffer mode of USB endpoint 2

//unsigned short volatile xdata UEP0_DMA? ? ? ?_AT_ 0x2448;? ?// endpoint 0&4 buffer start address, must even address, big-endian

EXTERN? UINT8XV UEP0_DMA_H? ? ?_AT_ 0x2448;? ?// endpoint 0&4 buffer start address high byte

EXTERN? UINT8XV UEP0_DMA_L? ? ?_AT_ 0x2449;? ?// endpoint 0&4 buffer start address low byte

#define pUEP0_DMA_H? ? ? ?PBYTE[0x48]

#define pUEP0_DMA_L? ? ? ?PBYTE[0x49]

#define UEP0_DMA? ? ? ? ? (unsigned short volatile) UEP0_DMA_H

#define pUEP0_DMA? ? ? ? ?PWORD[0x48]

//unsigned short volatile xdata UEP1_DMA? ? ? ?_AT_ 0x244A;? ?// endpoint 1 buffer start address, must even address, big-endian

EXTERN? UINT8XV UEP1_DMA_H? ? ?_AT_ 0x244A;? ?// endpoint 1 buffer start address high byte

EXTERN? UINT8XV UEP1_DMA_L? ? ?_AT_ 0x244B;? ?// endpoint 1 buffer start address low byte

#define pUEP1_DMA_H? ? ? ?PBYTE[0x4A]

#define pUEP1_DMA_L? ? ? ?PBYTE[0x4B]

#define UEP1_DMA? ? ? ? ? (unsigned short volatile) UEP1_DMA_H

#define pUEP1_DMA? ? ? ? ?PWORD[0x4A]

//unsigned short volatile xdata UEP2_DMA? ? ? ?_AT_ 0x244C;? ?// endpoint 2 buffer start address, must even address, big-endian

EXTERN? UINT8XV UEP2_DMA_H? ? ?_AT_ 0x244C;? ?// endpoint 2 buffer start address high byte

EXTERN? UINT8XV UEP2_DMA_L? ? ?_AT_ 0x244D;? ?// endpoint 2 buffer start address low byte

#define pUEP2_DMA_H? ? ? ?PBYTE[0x4C]

#define pUEP2_DMA_L? ? ? ?PBYTE[0x4D]

#define UEP2_DMA? ? ? ? ? (unsigned short volatile) UEP2_DMA_H

#define pUEP2_DMA? ? ? ? ?PWORD[0x4C]

//unsigned short volatile xdata UEP3_DMA? ? ? ?_AT_ 0x244E;? ?// endpoint 3 buffer start address, must even address, big-endian

EXTERN? UINT8XV UEP3_DMA_H? ? ?_AT_ 0x244E;? ?// endpoint 3 buffer start address high byte

EXTERN? UINT8XV UEP3_DMA_L? ? ?_AT_ 0x244F;? ?// endpoint 3 buffer start address low byte

#define pUEP3_DMA_H? ? ? ?PBYTE[0x4E]

#define pUEP3_DMA_L? ? ? ?PBYTE[0x4F]

#define UEP3_DMA? ? ? ? ? (unsigned short volatile) UEP3_DMA_H

#define pUEP3_DMA? ? ? ? ?PWORD[0x4E]

//EXTERN? UINT8XV UH_EP_MOD? ? ? _AT_ 0x2447;? ?// host endpoint mode

#define UH_EP_MOD? ? ? ? ?UEP2_3_MOD

#define pUH_EP_MOD? ? ? ?pUEP2_3_MOD

#define bUH_EP_TX_EN? ? ? 0x40? ? ? // enable USB host OUT endpoint transmittal

#define bUH_EP_TBUF_MOD? ?0x10? ? ? // buffer mode of USB host OUT endpoint

// bUH_EP_TX_EN & bUH_EP_TBUF_MOD: USB host OUT endpoint buffer mode, buffer start address is UH_TX_DMA

//? ?0 x:? disable endpoint and disable buffer

//? ?1 0:? 64 bytes buffer for transmittal (OUT endpoint)

//? ?1 1:? dual 64 bytes buffer by toggle bit bUH_T_TOG selection for transmittal (OUT endpoint), total=128bytes

#define bUH_EP_RX_EN? ? ? 0x08? ? ? // enable USB host IN endpoint receiving

#define bUH_EP_RBUF_MOD? ?0x01? ? ? // buffer mode of USB host IN endpoint

// bUH_EP_RX_EN & bUH_EP_RBUF_MOD: USB host IN endpoint buffer mode, buffer start address is UH_RX_DMA

//? ?0 x:? disable endpoint and disable buffer

//? ?1 0:? 64 bytes buffer for receiving (IN endpoint)

//? ?1 1:? dual 64 bytes buffer by toggle bit bUH_R_TOG selection for receiving (IN endpoint), total=128bytes

//unsigned short volatile xdata UH_RX_DMA? ? ? _AT_ 0x244C;? ?// host rx endpoint buffer start address, big-endian

#define UH_RX_DMA? ? ? ? ?UEP2_DMA

#define pUH_RX_DMA? ? ? ?pUEP2_DMA

//EXTERN? UINT8XV UH_RX_DMA_H? ? _AT_ 0x244C;? ?// host rx endpoint buffer start address high byte

#define UH_RX_DMA_H? ? ? ?UEP2_DMA_H

#define pUH_RX_DMA_H? ? ?pUEP2_DMA_H

//EXTERN? UINT8XV UH_RX_DMA_L? ? _AT_ 0x244D;? ?// host rx endpoint buffer start address low byte

#define UH_RX_DMA_L? ? ? ?UEP2_DMA_L

#define pUH_RX_DMA_L? ? ?pUEP2_DMA_L

//unsigned short volatile xdata UH_TX_DMA? ? ? _AT_ 0x244E;? ?// host tx endpoint buffer start address, big-endian

#define UH_TX_DMA? ? ? ? ?UEP3_DMA

#define pUH_TX_DMA? ? ? ?pUEP3_DMA

//EXTERN? UINT8XV UH_TX_DMA_H? ? _AT_ 0x244E;? ?// host tx endpoint buffer start address high byte

#define UH_TX_DMA_H? ? ? ?UEP3_DMA_H

#define pUH_TX_DMA_H? ? ?pUEP3_DMA_H

//EXTERN? UINT8XV UH_TX_DMA_L? ? _AT_ 0x244F;? ?// host tx endpoint buffer start address low byte

#define UH_TX_DMA_L? ? ? ?UEP3_DMA_L

#define pUH_TX_DMA_L? ? ?pUEP3_DMA_L

/*? LED Registers on xDATA, xSFR? */

#define REG_LED_BASE? ? ? 0x2880? ? // LED registers base address

EXTERN? UINT8XV LED_STAT? ? ? ?_AT_ 0x2880;? ?// LED status

#define pLED_STAT? ? ? ? ?PBYTE[0x80]

#define bLED_IF_DMA_END? ?0x80? ? ? // interrupt flag for DMA completion, write 1 to clear or write LED_DMA_CN to clear

#define bLED_FIFO_EMPTY? ?0x40? ? ? // ReadOnly: indicate FIFO empty status

#define bLED_IF_FIFO_REQ? 0x20? ? ? // interrupt flag for request FIFO data ( FIFO <=2), write 1 to clear

#define bLED_CLOCK? ? ? ? 0x10? ? ? // ReadOnly: current LED clock level

#define MASK_LED_FIFO_CNT 0x07? ? ? // ReadOnly: bit mask of LED FIFO count

EXTERN? UINT8XV LED_CTRL? ? ? ?_AT_ 0x2881;? ?// LED control

#define pLED_CTRL? ? ? ? ?PBYTE[0x81]

#define bLED_CHAN_MOD1? ? 0x80? ? ? // LED channel mode high bit

#define bLED_CHAN_MOD0? ? 0x40? ? ? // LED channel mode low bit

#define MASK_LED_CHAN_MOD 0xC0? ? ? // bit mask of LED channel mode

// bLED_CHAN_MOD1 & bLED_CHAN_MOD0: LED channel mode

//? ?00: single channel output, LED0

//? ?01: dual channels output, LED0/1

//? ?10: 4 channels output, LED0~3

//? ?11: 4 channels output and LED2/3 from aux buffer, LED0~3

#define bLED_IE_FIFO_REQ? 0x20? ? ? // enable interrupt for FIFO <=2

#define bLED_DMA_EN? ? ? ?0x10? ? ? // DMA enable and DMA interrupt enable for LED

#define bLED_OUT_EN? ? ? ?0x08? ? ? // LED output enable

#define bLED_OUT_POLAR? ? 0x04? ? ? // LED output polarity: 0=pass, 1=invert

#define bLED_CLR_ALL? ? ? 0x02? ? ? // force clear FIFO and count of LED

#define bLED_BIT_ORDER? ? 0x01? ? ? // LED bit data order: 0=LSB first, 1=MSB first

EXTERN? UINT8XV LED_DATA? ? ? ?_AT_ 0x2882;? ?// WriteOnly: data port

#define pLED_DATA? ? ? ? ?PBYTE[0x82]

//EXTERN? UINT8XV LED_FIFO_CN? ? _AT_ 0x2882;? ?// ReadOnly: FIFO count status

#define LED_FIFO_CN? ? ? ?LED_DATA

EXTERN? UINT8XV LED_CK_SE? ? ? _AT_ 0x2883;? ?// clock divisor setting

#define pLED_CK_SE? ? ? ? PBYTE[0x83]

//unsigned short volatile xdata LED_DMA? ? ? ? _AT_ 0x2884;? ?// DMA address, must even address, big-endian, automatic increasing after DMA

EXTERN? UINT8XV LED_DMA_AH? ? ?_AT_ 0x2884;? ?// DMA address high byte, automatic increasing after DMA

EXTERN? UINT8XV LED_DMA_AL? ? ?_AT_ 0x2885;? ?// DMA address low byte, automatic increasing after DMA

#define pLED_DMA_AH? ? ? ?PBYTE[0x84]

#define pLED_DMA_AL? ? ? ?PBYTE[0x85]

#define LED_DMA? ? ? ? ? ?(unsigned short volatile) LED_DMA_AH

#define pLED_DMA? ? ? ? ? PWORD[0x84]

EXTERN? UINT8XV LED_DMA_CN? ? ?_AT_ 0x2886;? ?// DMA remainder word count, just main buffer and exclude aux buffer, automatic decreasing after DMA

#define pLED_DMA_CN? ? ? ?PBYTE[0x86]

//unsigned short volatile xdata LED_DMA_X? ? ? _AT_ 0x2888;? ?// aux buffer DMA address, must even address, big-endian, automatic increasing after DMA

EXTERN? UINT8XV LED_DMA_XH? ? ?_AT_ 0x2888;? ?// aux buffer DMA address high byte, automatic increasing after DMA

EXTERN? UINT8XV LED_DMA_XL? ? ?_AT_ 0x2889;? ?// aux buffer DMA address low byte, automatic increasing after DMA

把ch559.H其中上述代码注释掉,代码就可以正常运行