为了正常使用必须给 I2C 输入正确的时钟,其中标准模式下,输入时钟最低为 2MHz,在快速模

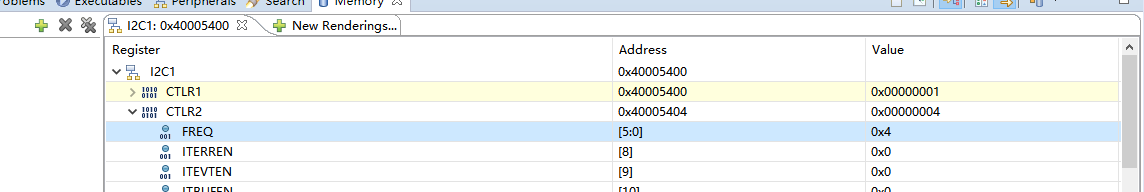

式下,输入时钟最低为 4MHz。但I2C1_CTLR2的FREQ[5:0]范围是8-48,是否能设为2-4I2C1_CKCFGR的CCR[11:0]分频系数该如何填写

I2C1_CTLR2的FREQ[5:0]牵扯到内部的延时,按照手册范围走,大了没关系,分频系数按照库函数配置就可以。一般库函数的时钟配置是APB1=系统主频,不会到达2M或者4M。

static void SetSysClockTo_24MHZ_HSI(void)

{

/* Flash 0 wait state */

FLASH->ACTLR &= (uint32_t)((uint32_t)~FLASH_ACTLR_LATENCY);

FLASH->ACTLR |= (uint32_t)FLASH_ACTLR_LATENCY_0;

/* HCLK = SYSCLK = APB1 */

RCC->CFGR0 |= (uint32_t)RCC_HPRE_DIV6;

}

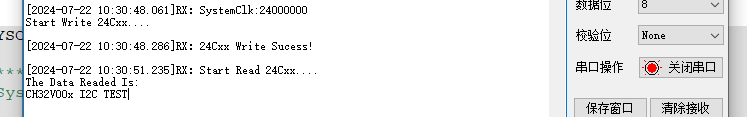

这边时钟配置24M/6=4M,我这样测试IIC没问题。

此时I2C1_CTLR2的FREQ[5:0]=4M。这样也没问题。

目前的情况是:主机发送写指令,写一个字节,然后发送repeated start ,读一个字节,之前写的字节不会触发RxNE中断导致接收不到这个字节

你好,具体邮箱联系我吧,zdg@wch.cn