使用ch32v305的sdio和fpga进行通信,不理会命令通道的交互,只用sdio的数据通道对fpga进行读写操作。

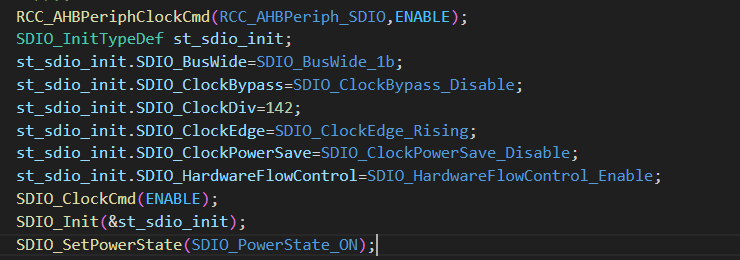

在1位数据线,stream模式,1MHz的时钟速率,进行以下初始化

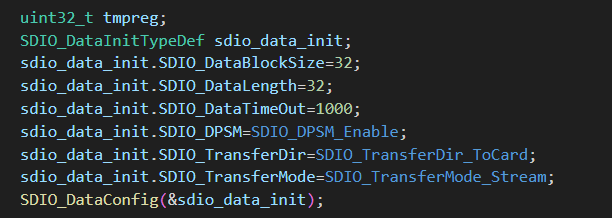

向fpga进行写操作,用逻辑分析仪能够观察到正常的全部32字节的写入;

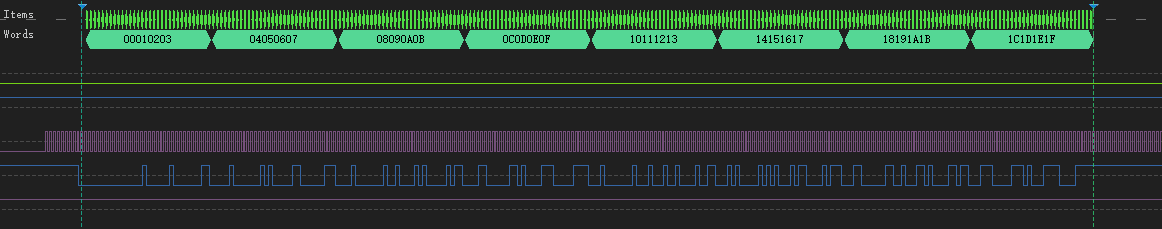

但是使用4位或者8位数据宽度,发出来的数据是错乱的,数据长度也不对,而且会“重发”。

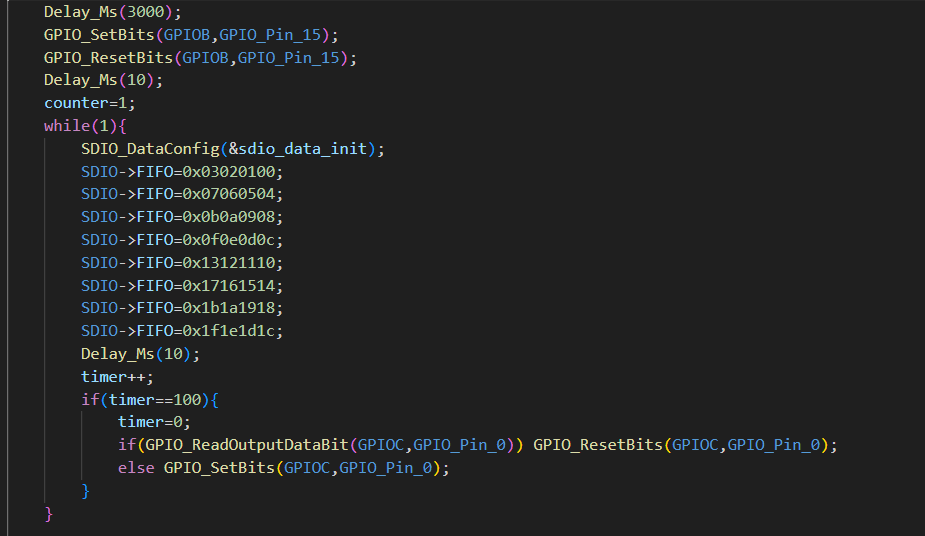

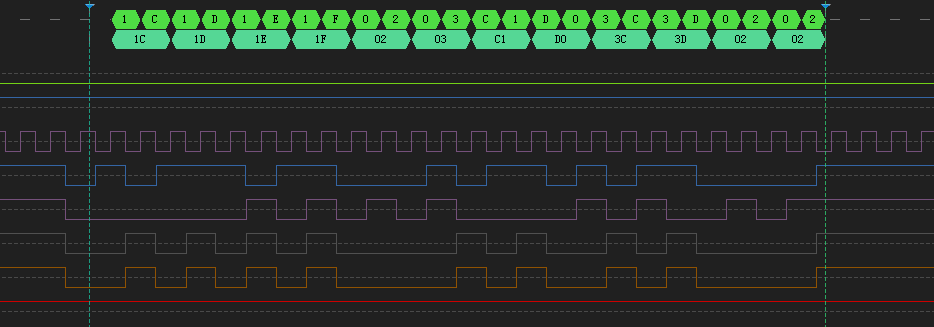

如下图所示,预期发送的数据是32个0xf0f0f0f0,但是逻辑分析仪捕捉结果是:

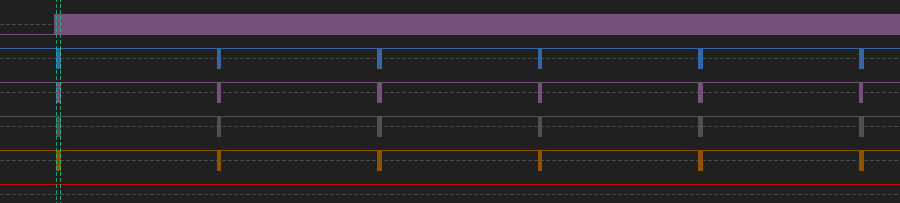

这就是出现的数据重发的数据波形(上图是下图其中一段放大后的结果):

每两个数据发送之间的时间间隔就是代码中设置的“数据超时时间”,sdiodatatimeout,1000个sdio时钟周期,测出来是1ms左右。

是不是4位和8位数据模式需要有特殊的设置?

又或者是,即便在sdio主机在stream模式发送数据的过程中,也需要从机通过cmd或者data通道进行应答?