Hi,

I have issues with CH344Q chip.

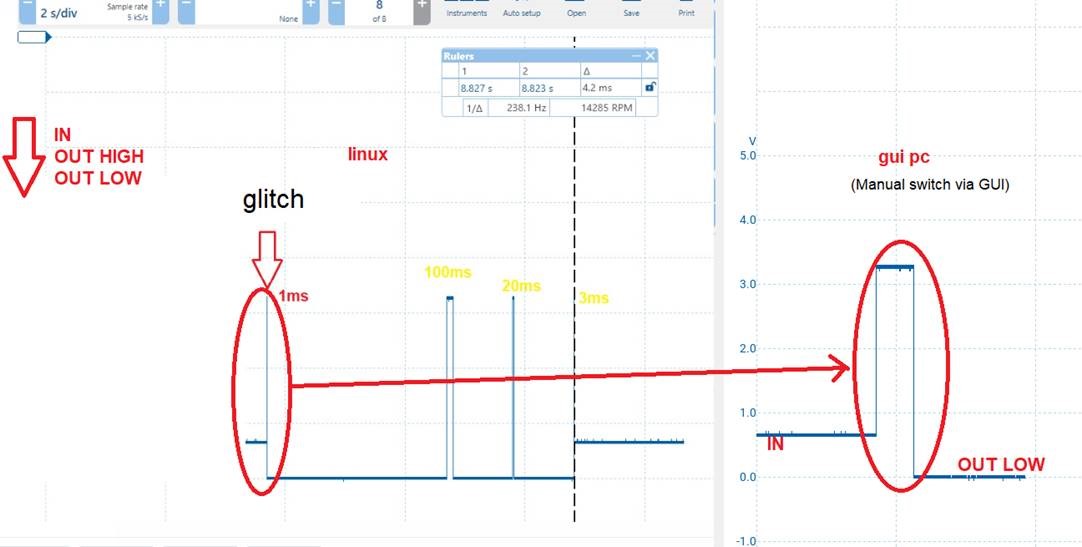

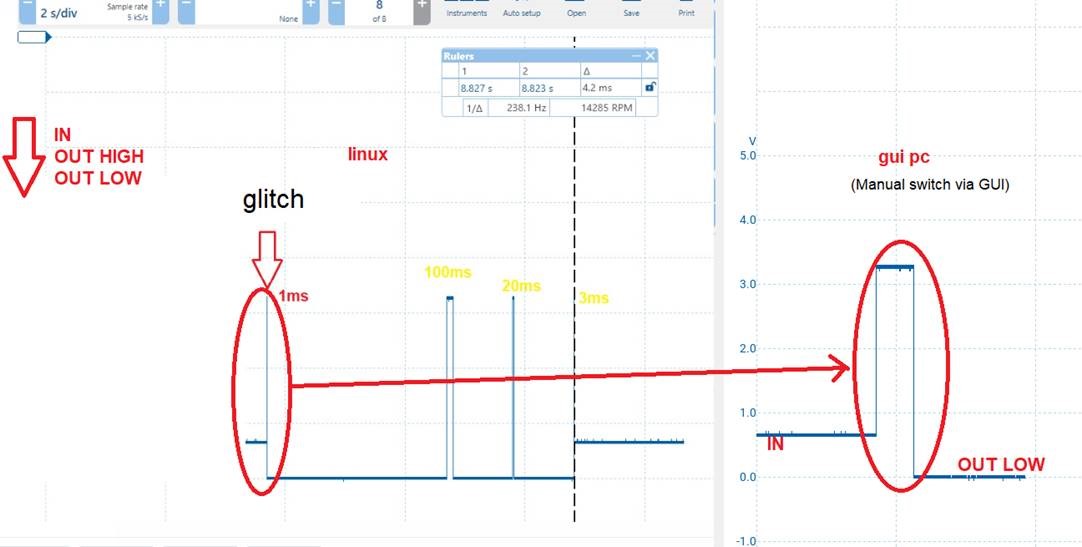

I use GPIO0 with PD=10K, when I produce 3 pules (100ms, 20ms, 3ms) I have parasitic glitch at beginning.

In driver I should go through IN -> OUT HIGH -> OUT LOW sequence.

How can I remove the glitch in software ?

Hi,

I have issues with CH344Q chip.

I use GPIO0 with PD=10K, when I produce 3 pules (100ms, 20ms, 3ms) I have parasitic glitch at beginning.

In driver I should go through IN -> OUT HIGH -> OUT LOW sequence.

How can I remove the glitch in software ?

Hello,The problem is caused by the addition of a pull-down resistor. What is the purpose of adding a 10K pull-down resistor.

Hi,

Yes, we need "0" at power up, so I add PD 10K for sure that there will no any noise.

Hello,You can configure DTR0-3 as a TNOW pin function, which defaults to a low level when powered on, and then configure these IO pins as GPIO output pins.

Hello

Yes, I know about DTR0-3 pins, but this pin - GPIO0 - is not part of them...

Any other solution may be ?

Pavel.

Hi

Please update - any other solutions for our problem ?

Hello,

Reply to the question in the email:

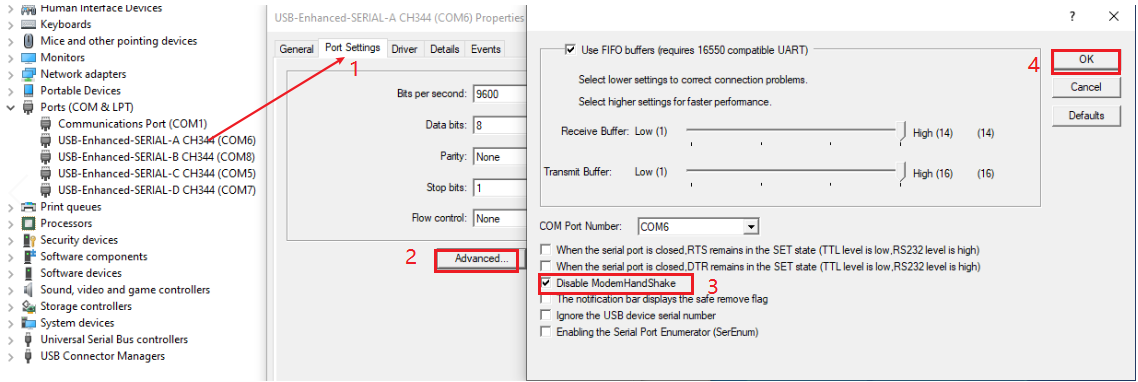

Problem 1: Opening the serial port will cause the RTS and DTR to slow down for several tens of microseconds. You can disable modemhandshake function, as shown in the following figure.

Problem 2: When opening the serial port to send data, there will be many unwanted pulses. Please confirm whether the DTR pin is switched to TNOW function. If it is DTR function, you can send data at intervals and use an oscilloscope to observe whether the DTR unwanted pulses is normal during the period of no data transmission, in order to rule out whether the DTR unwanted pulses fluctuation is caused by TXD signal interference.