I have written some testcode for a device which can be powered at 5V and at 3.3V.

see: power ch552 with 5 or 3.3V - 沁恒微电子社区 (wch.cn)

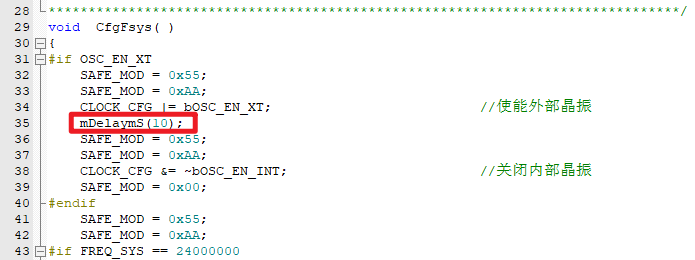

In my design i am using a delay loop similar to debug.c to generate a 320us delay. I have adjusted the loopvar so i can reach 321us with a loop value of 316. Fsys is set to 12MHz. So far it works as expected.

Then I added code to switch off the internal LDO because I have a external 3.3 regulator in my design.

With the external LDO and internal LDO switched off my delay loop is 347us. This is independed from 3.3V or 5V mode. If i dont switch off the internal LDO its stable at 321us in both modes.

So when the internal LDO is switched off my delay gets allmost 30us slower. My fsys is slower which should not be too much of a problem, but i fear that my USB device will not work. Is it possble that the external LDO can change the PLL when the internal LDO is off?

Any insights are welcome.

void main(void)

{

SAFE_MOD = 0x55;

SAFE_MOD = 0xAA;

GLOBAL_CFG |= bLDO3V3_OFF; //switch off internal LDO

clockInit();

while(1)

{

clockWait(1); //321us or 347us on bLDO3V3_OFF

P1_6 = ! P1_6;

}

}