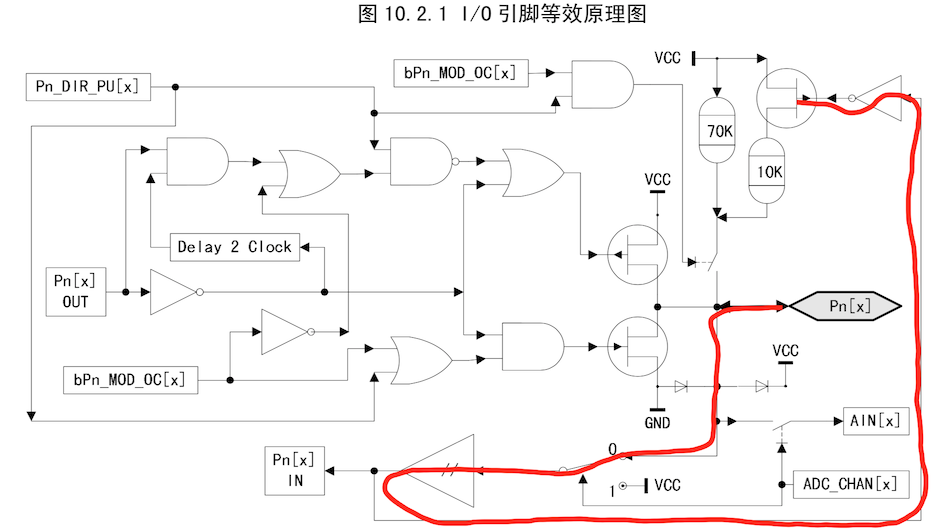

我最近在试图把5V CH552和3.3V系统相连,想试着用标准51模式省掉电平转换。发现IO口有两个上拉电阻,其中一个还是受PMOS控制的。我观察了一下,电阻和开通与否受外部电压影响。于是我用一个电位器测量IO口的电流。得到以下结果

0V~2V 0.062mA

2V跳变后 0.365mA

2.5V 0.354mA

3V 0.32mA

3.5V 0.265mA

4V 0.2mA

4.5V 0.1mA

5V 0mA

跳变的电压介于VIL5的最大值和VIH5的最小值之间,可以理解。但是这个10K电阻有何用意?是否在电路设计上有什么需要注意的问题? 我能想到是为了省电,以及形成滞回的效果?

热门产品 :

CH390:以太网控制器芯片