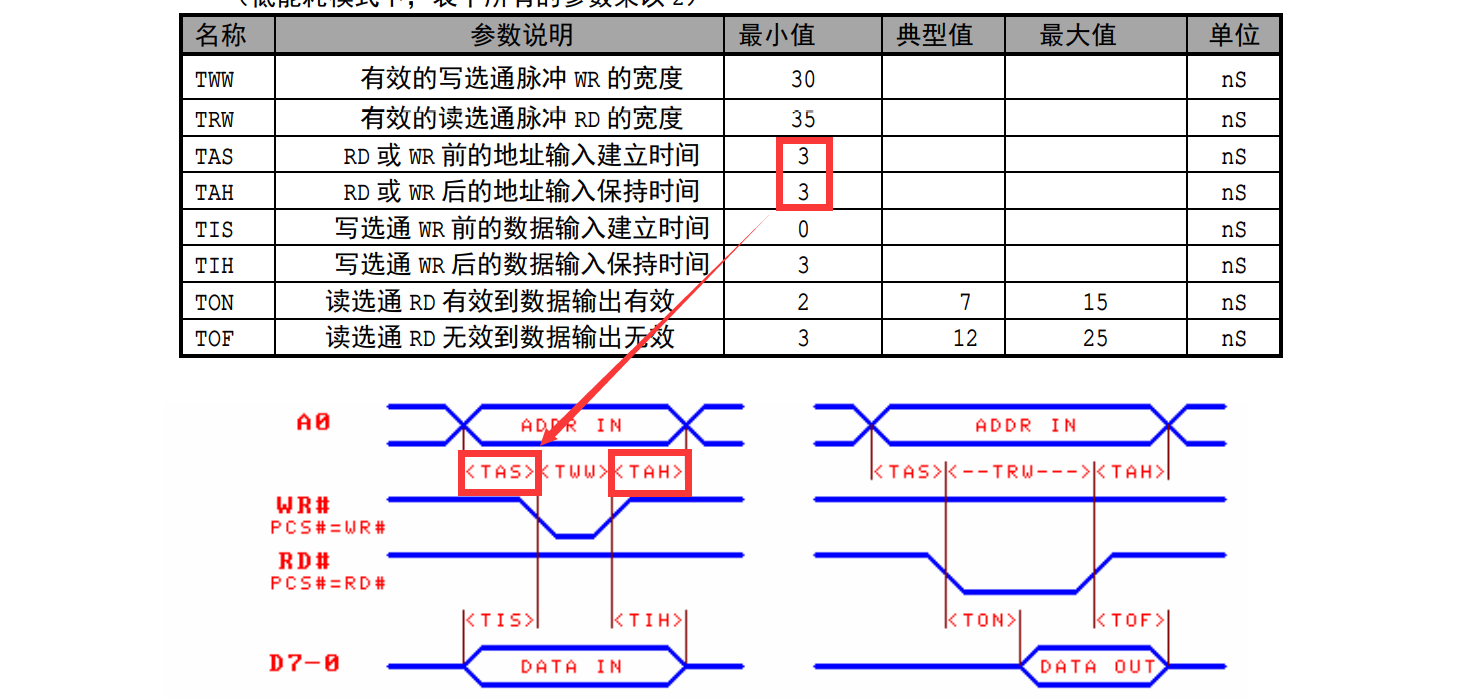

如上图TAS、TAH有最小3ns的约束

1, 在保证WR, RD低电平够宽的情况下(35),能否在设置A0的同时拉低WR#, RD#, PCS#

2, 文档中没有找到PCS#的约束,所以我想知道PCS是否可以与WR, RD在同一个时钟沿设置

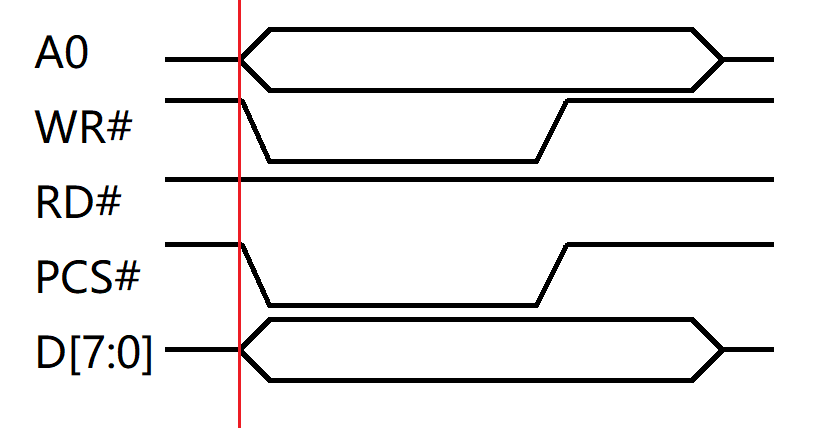

期望时序如下:

热门产品 :

CH397: 高集成度、低功耗USB网卡芯片

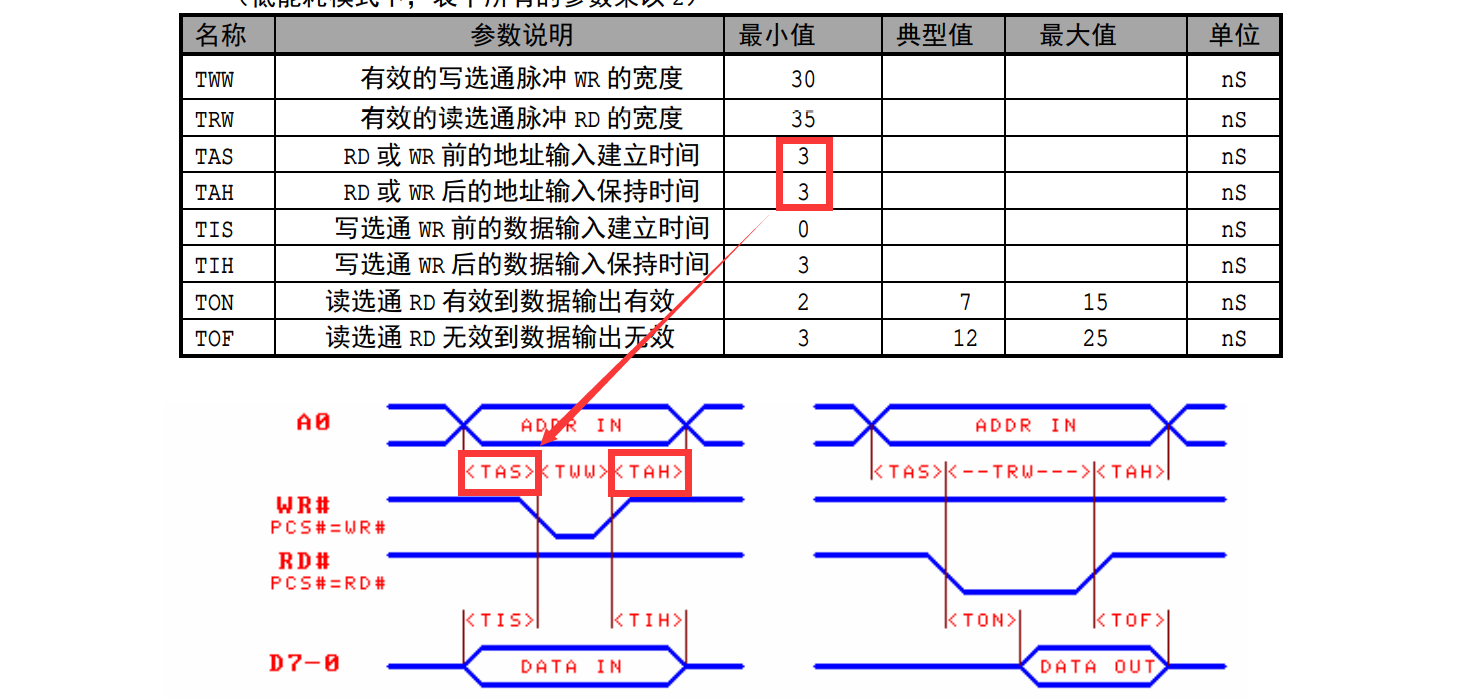

如上图TAS、TAH有最小3ns的约束

1, 在保证WR, RD低电平够宽的情况下(35),能否在设置A0的同时拉低WR#, RD#, PCS#

2, 文档中没有找到PCS#的约束,所以我想知道PCS是否可以与WR, RD在同一个时钟沿设置

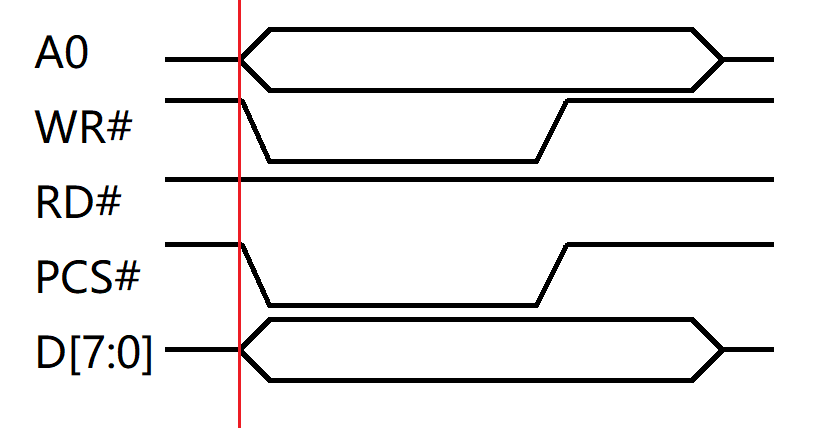

期望时序如下:

您好,建议PCS拉低后,再进行WR,RD 信号操作。