想了解一下RISC-V3A架构,主要是和标准RISC-V架构相比之下的增强,感觉比较有意思。

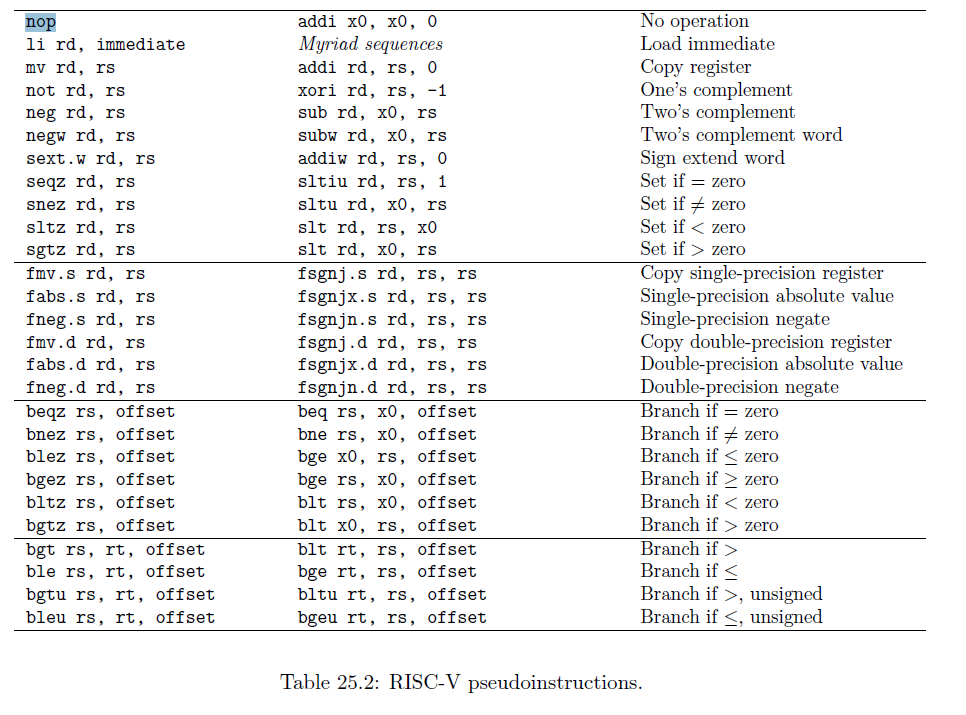

标准RISC-V没有NOP指令,但是CH573的代码中有__nop()函数,实际是通过汇编调用了NOP指令。

还有RISC-V3A还支持硬件压栈,也比较有意思。

热门产品 :

CH592: RISC-V内核BLE5.4无线MCU

想了解一下RISC-V3A架构,主要是和标准RISC-V架构相比之下的增强,感觉比较有意思。

标准RISC-V没有NOP指令,但是CH573的代码中有__nop()函数,实际是通过汇编调用了NOP指令。

还有RISC-V3A还支持硬件压栈,也比较有意思。

1、RISC-V3A 为沁恒自研RISC-V内核,支持标准RV32IMAC指令集,详细规范可参考RISC-V官方文档:https://riscv.org/technical/specifications/

2、RISC-V支持nop伪指令,对应addi x0, x0, 0,见riscv-spec手册,

3、RISC-V3A内核支持硬件压栈(HPE)和免表中断(VTF),配合编译器MounRiver Studio(MRS)编译后,可提升中断响应时间。