HCLK配置成了120MHZ

PCLK1=60MHZ

PCLK2=120MHZ

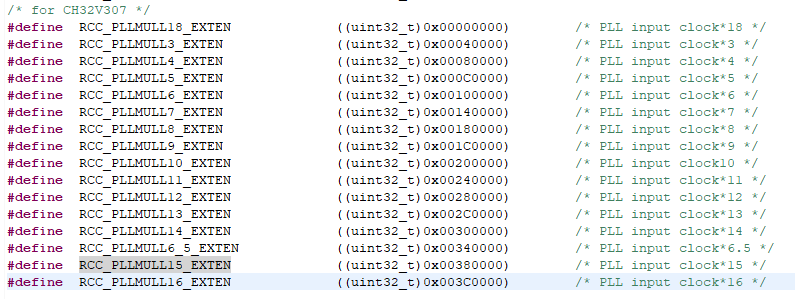

adc_clk只能是PCLK2的 2、4、6、8分频,那这样子adc_clk最小也是15MHZ了,大于ADC时钟的最大值(14MHZ);

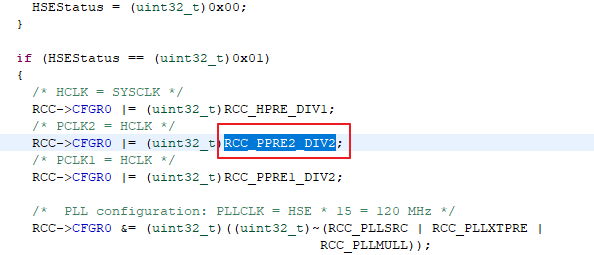

现在只能回头去static void SetSysClockTo120(void)里改PCLK2的值了,

有其它更方便的方法么?就是不要动WCH提供的库函数文件。

热门产品 :

CH592: RISC-V内核BLE5.4无线MCU