在研究V203使用时钟的时候,发现了个设置问题。

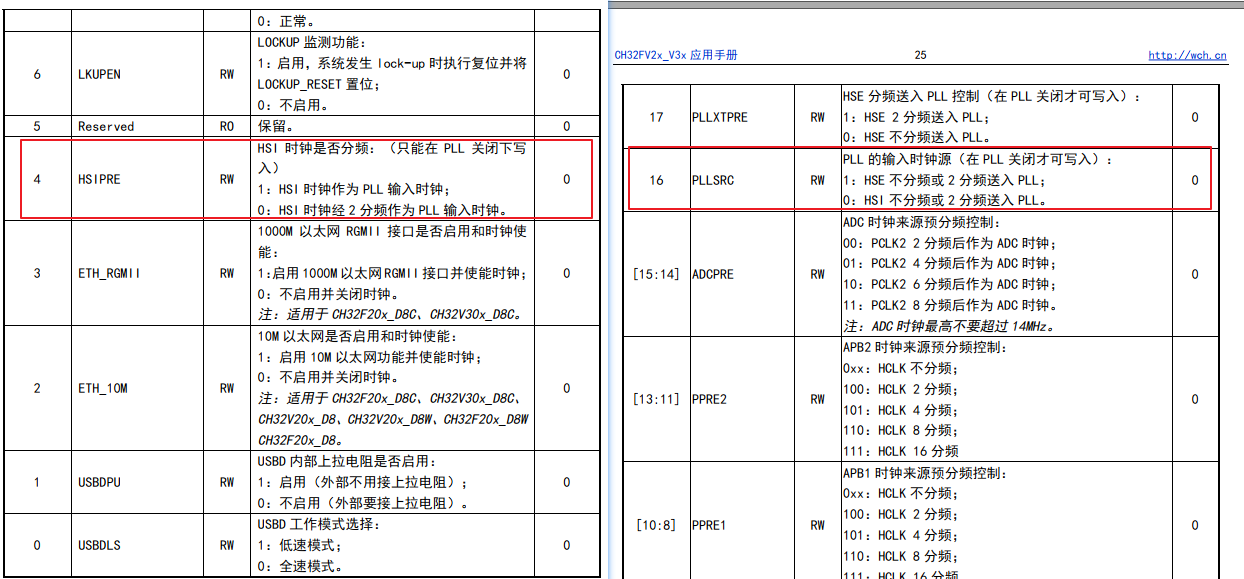

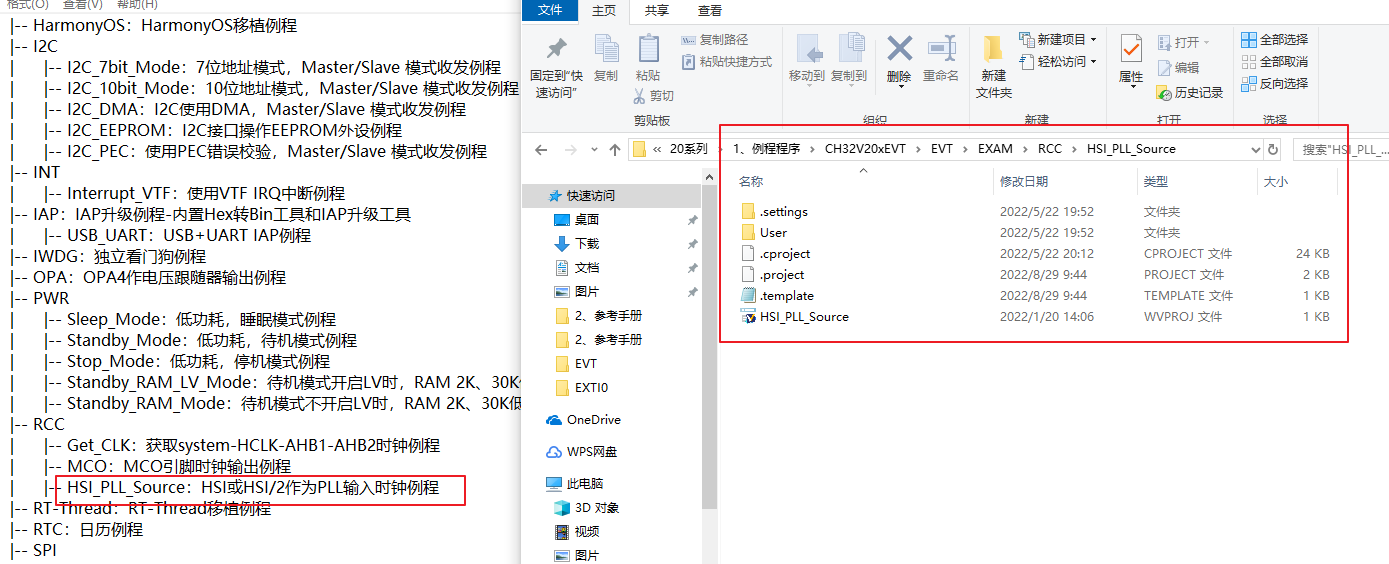

看手册HSI到PLL是可以选择不分频或者二分频,关于这个分频有两个地方提及,一个是EXTEND_CTR寄存器的bit4,一个是RCC_CFGR0寄存器的bit16,根据 EVT的示例,看出来官方是做了 EXTEN->EXTEN_CTR |= EXTEN_PLL_HSI_PRE; RCC->CFGR0 |= (uint32_t)(RCC_PLLSRC_HSI_Div2 | RCC_PLLMULL18);

这里的疑惑是EXTEN_CTR的bit4被置1了,对应为HSI 时钟作为 PLL 输入时钟,后面又写的是RCC_PLLSRC_HSI_Div2,但是手册里相关的位解释是HSI不分频或者2分频送入pll,这里认为解释较为模糊,因为在exten_ctr里并没有使能2分频。

请官方对上述问题阐述一下,并下面相关疑问做一下回复

1、能否给出一个完备的HSI预分频部分的解释或者示例(包括HSI不分频进入PLL和HSI 2分频进入PLL)

2、关于ch32v20x.h文件里 对于PLLSRC的宏定义有歧义,因为只有RCC_PLLSRC_HSI_DIV2和RCC_PLLSRC_HSE,难道这里的意思是使用HSI时 PLLSRC固定为HSI的二分频?