/* PLL configuration: PLLCLK = HSI * 6 = 48 MHz */

RCC->CFGR0 &= (uint32_t)((uint32_t)~(RCC_PLLSRC | RCC_PLLXTPRE | RCC_PLLMULL));

#ifdef CH32V30x_D8

RCC->CFGR0 |= (uint32_t)(RCC_PLLSRC_HSI_Div2 | RCC_PLLMULL6);

#else

RCC->CFGR0 |= (uint32_t)(RCC_PLLSRC_HSI_Div2 | RCC_PLLMULL6_EXTEN);

#endif

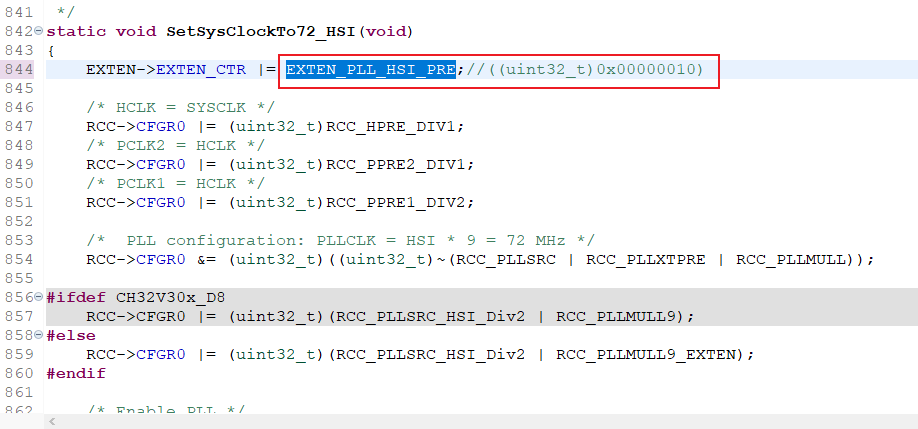

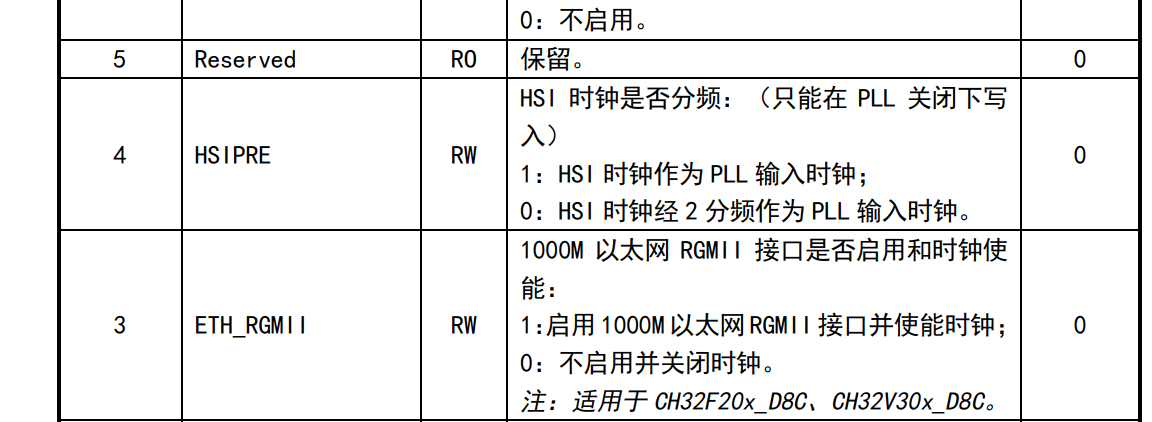

wch 提供的例子: RCC_PLLSRC_HSI_Div2 RCC_PLLMULL6 为什么不是 HSI/2*6

而是 HSI*6