想要双ADC多通道的采样频率达到250kHz 采用的是同步规则的模式

于是选用了定时器控制以为了可以精确的达到这么高的频率

考虑到多通道总共的转换时间需要包含在一个周期内

选择了1.5的周期的模式ADC_SampleTime_1Cycles5 但是采样出的数据就不正确

改成38.5就正确 但38.5周期的采样时间 会不会实际就达不到250kHz的采样频率?

想要双ADC多通道的采样频率达到250kHz 采用的是同步规则的模式

于是选用了定时器控制以为了可以精确的达到这么高的频率

考虑到多通道总共的转换时间需要包含在一个周期内

选择了1.5的周期的模式ADC_SampleTime_1Cycles5 但是采样出的数据就不正确

改成38.5就正确 但38.5周期的采样时间 会不会实际就达不到250kHz的采样频率?

您好,

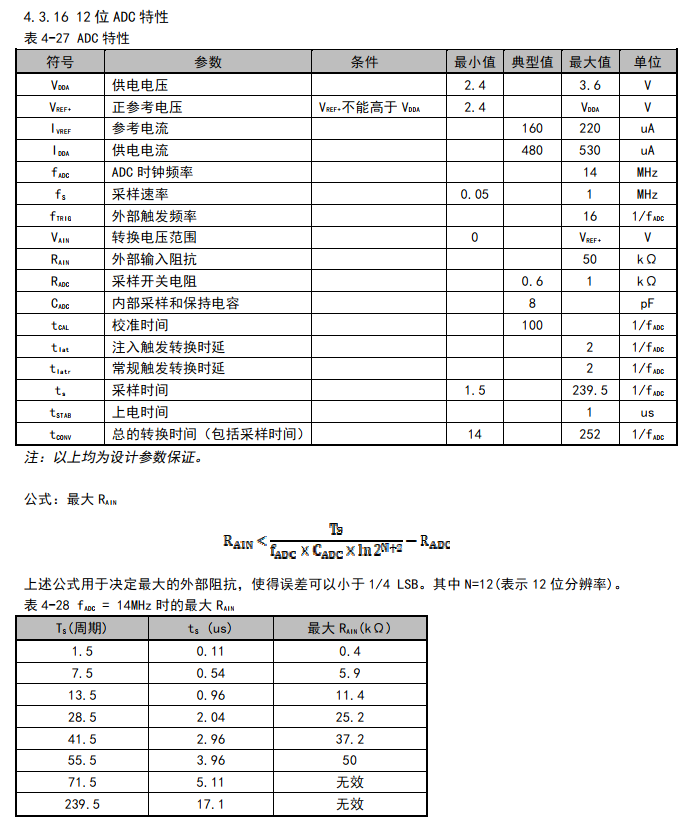

在芯片数据手册中,给出了ADC的相关参数,可以据此进行计算。

采样时间选择1.5周期时,要注意外部阻抗的匹配问题。

附件中是CH32V203C8T6,使用定时器2触发,双ADC快速交替,单通道采样的程序,您可以根据实际需要做出修改。

如果依然存在使用问题,可以通过邮件和我联系。(邮箱:lbw@wch.cn)

![]() CH32V203C8T6_Time2_DualADC_FastInterleaved_2022.11.zip

CH32V203C8T6_Time2_DualADC_FastInterleaved_2022.11.zip

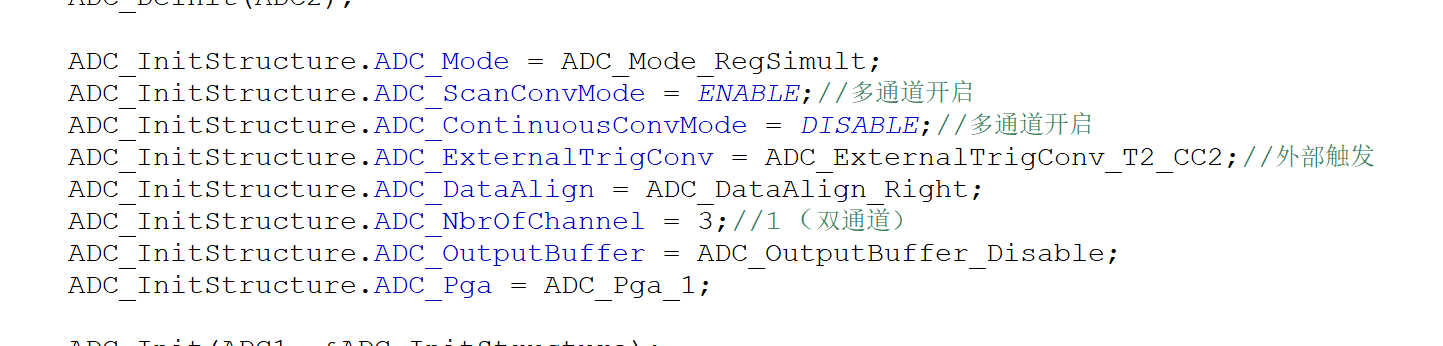

您好,我设计的是双ADC各三个通道总共六通道

双ADC快速交替模式,的确可以提高采样速率,但六个通道是不是无法使用这种模式

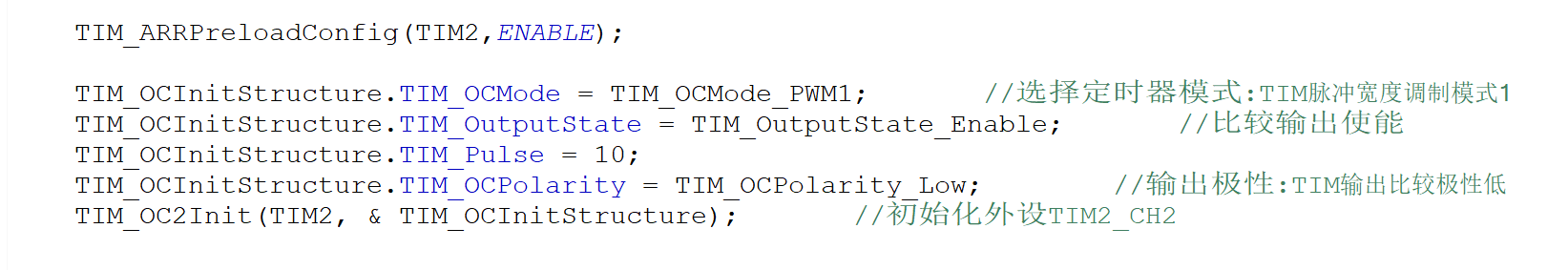

我看您提供的例程中 直接都是软件触发的模式,我是这样写的

选择的是这种外部触发的方式

您好,

双ADC快速交替的方式,往往只对一个通道使用,我们芯片的应用手册中,对这一方法有较为详细的描述。

之前我对您的描述,存在理解上的偏差。按照您的想法,应该是在一定的周期内,需要采集6个通道的数据,希望使用2个ADC,每个ADC负责三个通道的采集。

我出于快速完成测试的目的,直接在中断函数中,使用了软件的方式,完成ADC采样的触发,所以在触发方式的选择上不必纠结,只要能够稳定的触发两个ADC采样即可。

如果方便的话,可以将包含ADC采样部分的工程、ADC外围电路的原理图发送至我的邮箱。