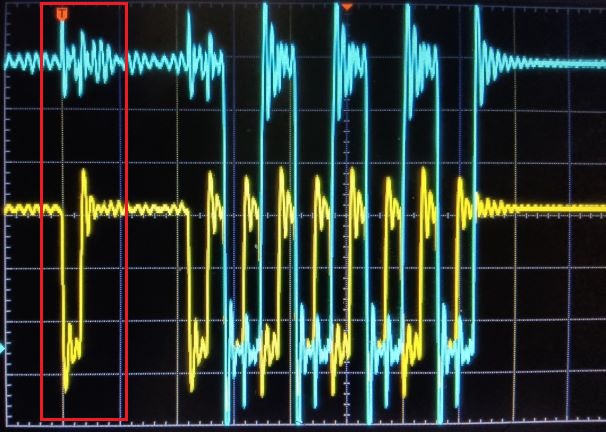

为什么在调用CH551G的SPI时,会在SCK前面出一个低电平?

而且需要后插3个nop才能保证SCK输出时钟数量和电平的正常?

![]()

以下是C代码和用SDCC编译后的汇编:

(用论坛自带的插入代码功能总会把半角空格变成问号,只好打个zip提交上来。字符集编码为UTF-8)

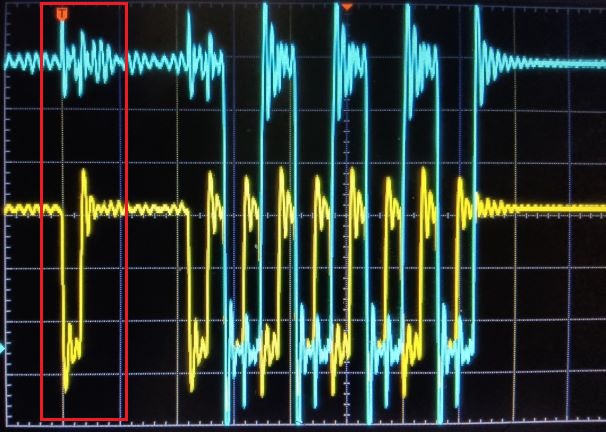

为什么在调用CH551G的SPI时,会在SCK前面出一个低电平?

而且需要后插3个nop才能保证SCK输出时钟数量和电平的正常?

![]()

以下是C代码和用SDCC编译后的汇编:

(用论坛自带的插入代码功能总会把半角空格变成问号,只好打个zip提交上来。字符集编码为UTF-8)

您好,

建议先测试单一SPI外设是否存在问题,检查该SCK引脚是否存在与其他功能复用,硬件处理上,检查该脚是否和其他器件相关。

C代码就只有这些,没有其他代码

使用的只有SPI外设

SCK引脚没有与其他功能复用

硬件只有一个CH551G,引脚输出直接接的示波器探头

well your code is very strange

check the clock programming i would do something like

CLOCK_CFG = (CLOCK_CFG & ~MASK_SYS_CK_SEL) | 0x06;

for sending spi data:

while (!S0_FREE)?

{

? ; /* wait till free */

}

SPI0_DATA? ? =? 0xAA;

摸索出解决办法了,但是为什么这样能解决?

先设置IO模式

P1_MOD_OC = 0x00 ;

P1_DIR_PU = 0xFF ;

P3_MOD_OC = 0x00 ;

P3_DIR_PU = 0xFF ;

再开启并设置SPI0外设

SPI0_CK_SE = 0x02 ;

SPI0_CTRL = 0x68 ;

即使是给GPIO先置全1,也还会在SCK前面出一个低电平,出错。

先开启并设置SPI0外设

SPI0_CK_SE = 0x02 ;

SPI0_CTRL = 0x68 ;

再设置IO模式

P1_MOD_OC = 0x00 ;

P1_DIR_PU = 0xFF ;

P3_MOD_OC = 0x00 ;

P3_DIR_PU = 0xFF ;

就不会在SCK前面出一个低电平,完全正常。

需要后插3个nop才能保证SCK输出时钟数量和电平的问题使用发送完成检测解决。

但是为什么先开启并设置SPI0外设,再设置IO模式,就能解决这个问题?

但是为什么先开启并设置SPI0外设,再设置IO模式,就能解决这个问题?

但是为什么先开启并设置SPI0外设,再设置IO模式,就能解决这个问题?

(重要的事说三遍)

不妨贴一下你现在完整的代码工程。

最初的压缩包里的代码工程就是全部,仅仅只是修改了这些代码的顺序

确认是老版本PlatformIO自带的SDCC版本有问题,更新到最新的PlatformIO和最新的SDCC后,再编译工程,顶楼的代码即使更换代码顺序后也会发生同样的问题。

使用最新的PlatformIO和最新的SDCC,先开启并设置SPI0外设,再设置IO模式。将后插3个nop,更换为while ( S0_FREE == 0 ) ;后,SPI0正常工作。