CH569常被用于和FPGA通信,利用自身USB3.0接口和电脑通讯,实现数据的高速收发。

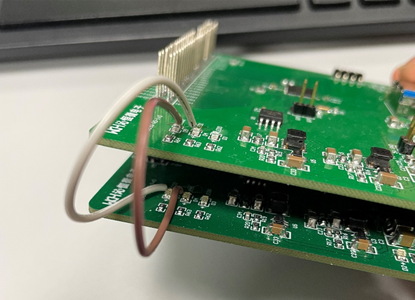

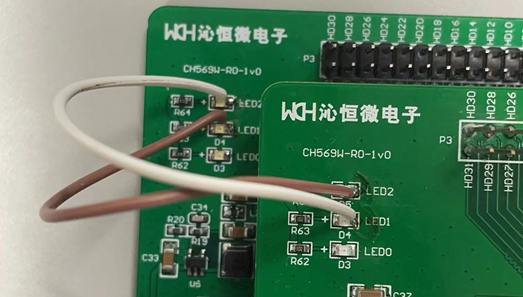

在实际使用中,我们需要对CH569评估板进行一些小改动。

????????用导线将上下两层板子的LED1和LED2的阴极交叉焊接到一起,这个在代码中会作为数据流控的状态指示引脚来使用(对应PB23和PB22,可以任意修改为其他空闲引脚)。加上32位宽HSPI接口的40个PIN,在实际使用时总共用到42根PIN来和FPGA对接。

?

????????CH569评估板上的SPI FLASH,不担任存储CH569固件的工作,只是作为一个SPI从机,方便使用者探究CH569的SPI外设,而已。所以在设计电路时,这个SPI FLASH直接去掉。CH569的固件是储存在片内flash上,启动也是内部加载。CH569最小系统只需要一颗晶振和阻容件即可实现。

以下是最小系统电路:

以下是和FPGA对接的推荐电路:

?

注意:

1、使用HSPI时设计下载按钮是PA13,因为默认的BOOT触发引脚PA5作为HSPI数据线HD0,为了优化走线,采用了备用的BOOT触发引脚。

2、芯片VDDIO网络供电电压可以降低至1.8V,以满足常见的FPGA IO电压。此处注意CH569芯片上电期间需要保持VDDIO最低为2.5V,待用户程序运行之后,再降低至目标电压。

3、HSPI的40根线尽可能做等长。

?